|

|

PDF YSS950 Data sheet ( Hoja de datos )

| Número de pieza | YSS950 | |

| Descripción | DAP1 Digital Audio Processor | |

| Fabricantes | YAMAHA | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de YSS950 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

YSS950

DAP1

Digital Audio Processor

■ Outline

The YSS950 (DAP1) is a DSP (Digital Signal Processor) for sound field processing, which features a

high-speed/ high-precision 32-bit floating point DSP.

■ Features

{ 32-bit floating point DSP achieves high-speed/high-precision operations

• Operation frequency: Approximately 166 MHz

• Data bus width: 32 bits (24-bit mantissa, 8-bit exponent)

• Multiplier/adder: 32 bits × 32 bits + 55 bits → 55 bits (47-bit mantissa, 8-bit exponent)

{ 48 KB (12 Kword) preset command code firmware area

{ 24 KB (6 Kword) download command code firmware area (maximum)

{ 104 KB (26 Kword) data RAM area (maximum)

{ High-speed command code/coefficient data firmware download (burst transfer)

{ Download coefficients data firmware without any interruption of sound (runtime transfer)

{ Firmware’s placement order can be changed

{ Firmware’s number of execution channels can be changed (up to 16 channels)

{ Multiple firmware calls are enabled

{ Audio I/O

• 32 bits × 16 channels, TDM

• Fixed point decimal format and floating point decimal format (IEEE Standard 754, two’s complement)

• Sampling frequency range is 32 to 192 kHz

• Audio clock division/switch

• Input/output muting

• Input/output channel switching

{ External memory not required

{ General I/O ports (4)

{ On-chip PLL

{ Power supply voltage: 1.2 V (core), 3.3 V (pin)

{ Low power consumption: Approximately 130mW (typical value)

{ Si-gate CMOS process

{ Lead-free 64-pin SQFP package (YSS950-SZ)

■ Applications

{ Home theater systems

{ Car audio

www.DataSheet4U.com

YSS950 CATALOG

CATALOG No.: LSI-4SS950A22

2006.10

1 page

YSS950

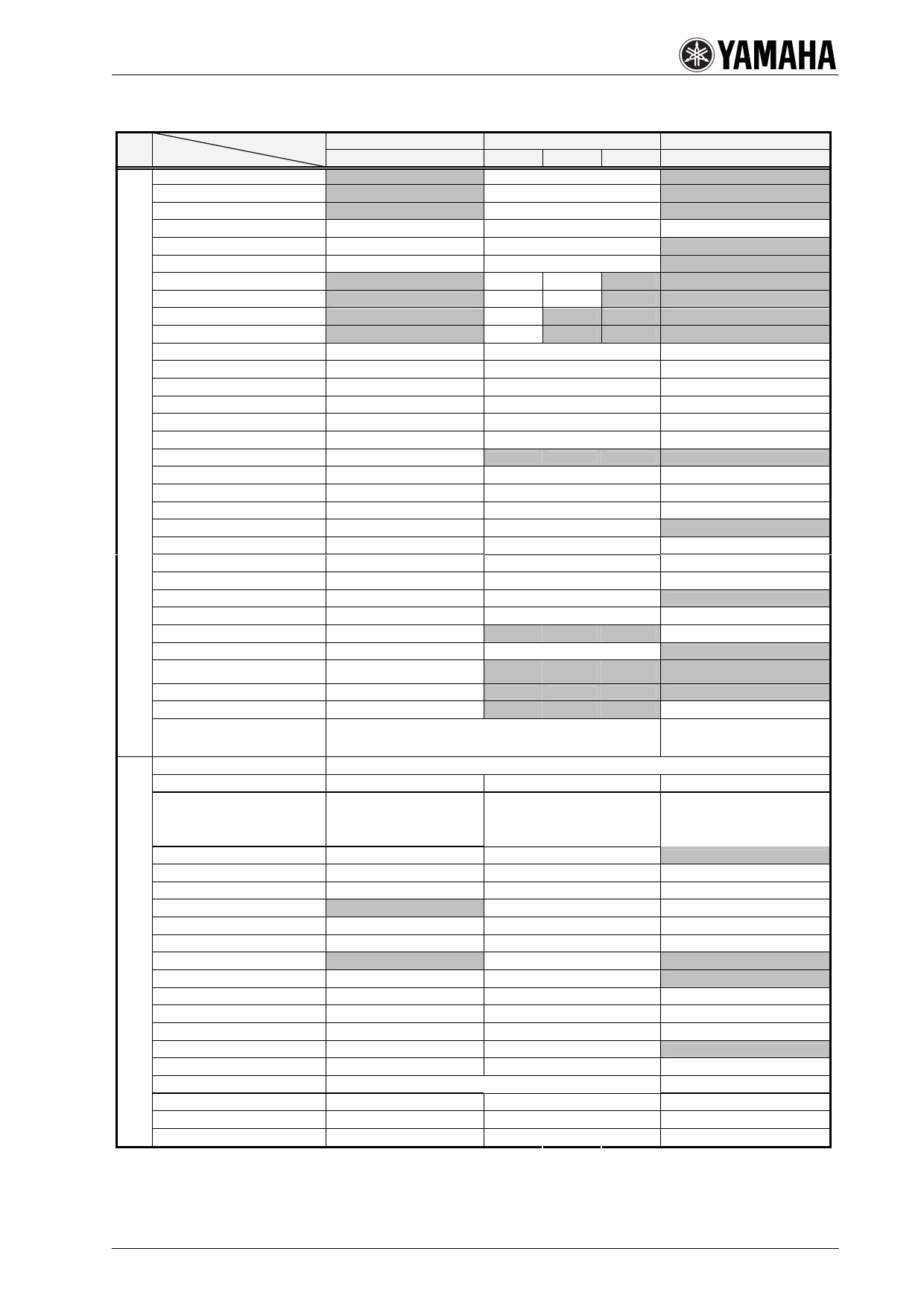

■ Comparison of Yamaha audio DSP

Chip Name

Function

Dolby digital decoding

Dolby Digital EX decoding

AAC decoding

PCM input playback

Dolby Pro Logic II decoding

Dolby Pro Logic IIx decoding

DTS decoding

DTS 96/24 decoding

DTS-ES decoding

DTS Neo:6 decoding

Tone control

Bass management

Volume adjustment

Noise generation

Impulse generation

Dynamic range controller

Harmonics regenerator

Nch surround

Sound field

Virtual surround

Headphone surround

Parametric equalizer

Graphic equalizer

Channel divider

Automatic acoustic calibration

Down mixing

Mixer

Down sampling

DAP1

YSS950

N

N

N

Y (up to 16 channels

Y

Y

N

N

N

N

Y

Y

Y

Y

Y

Y

Y

Y (Mixer)

Y

Y

Y

Y (8ch x 8Band x X)

Y (PEQ implementation)

Y

Y

Y (Mixer)

Y

Y (16 channels)

ADAMB

YSS944

YSS943

Y

Y

Y

YSS940

Y (up to 8 channels

Y

Y

YYN

YYN

YNN

YNN

Y

Y

Y

Y

Y

Y

N

Y

Y

Y

Y

Y (8ch x 5Band)

Y (PEQ implementation)

Y

Y

Y

N

Y (2 channels)

EVE

YSS920B

N

N

N

Y (up to 16 channels)

N

N

N

N

N

N

Y

Y

Y

Y

Y

Y

N

Y(Channel Distributor)

Y

Y

N

Y (5ch x 3Band)

Y(2ch x 10band)

Y

N

Y

Y

N

Modification of firmware placement

Y

N

N

Multiple firmware calls

User programmability

Precision of calculations

Microcontroller interface

Y

Y (design with module)

N

N

Internal data bus:32-bit floating point (24-bit mantissa, 8-bit exponent),

Coefficient : 32-bit floating point

Four-wire serial interface

N

Y(design with assembler)

Internal data bus:32-bit floating point

(28-bit mantissa, 4-bit exponent),

Coefficient : 16-bit fixed point

Firmware download

Y

Y

Digital audio interface

24 bits (fixed) or 32 bits

(floating) × 16 channels,

TDM (4 channels or 8 channels)

is enabled

24 bits (fixed) ×8 channels

Audio data channel switching control

Y (input and output)

Y (output)

Bypass

YY

User mute

Y (input and output)

Y (output)

External memory interface N SRAM (4Mbit)

Input delay (lip sync)

Y

Y

Output delay

YY

Stream detection

NY

Auto mute

YY

Status port

Auto mute, interrupt

Zero detection, auto mute, interrupt

General-purpose I/O ports

4

8

Internal operation clock generator

Y

Y

Power-up/power-down

Y

Y

Operation frequency

165.888 MHz

178.176MHz

Power supply voltage

1.2V (core), 3.3V (pin)

Power consumption (Typ.)

130 mW

211mW (Dolby Digital decoding)

Package

SQFP64

LQFP144

Lead-free

YY

Y

24 bits (fixed) or 32 bits (floating) ×

16 channels

N

Y (realize by firmware)

Y (output)

DRAM or SRAM (4Mbit)

Y

Y

N

N

Zero detection, etc

20

Y

N

50MHz

2.5V (core), 3.3V (pin)

165mW

SQFP100

Y

[Caution]

“Dolby”, “Dolby Pro Logic II”, and “Dolby Pro Logic IIx” are trademarks of Dolby Laboratories.

“DTS”, “DTS-ES”, “DTS-96/24”, and “DTS Neo:6” are trademarks of Digital Theater Systems, Inc.

5

5 Page

YSS950

■ FUNCTION DESCRIPTION

1 Serial Peripheral Interface

This LSI provides a four-wire serial peripheral interface (SPI) for the /CS, SK, SI, and SO pins.

microcontroller accesses the following via this serial peripheral interface

• Register address

• On-chip memory access (firmware download)

The following is a status transition diagram for the serial peripheral interface.

/CS=L

Register settings for

on-chip memory access

The

Device

not selected

Register access

/CS=H

/CS=H

On-chip

memory access

(Firmware download)

[Note]

In this manual, “register access” is the means of accessing on-chip memory, and should be considered as

functionally similar to “firmware download”.

(a) Register access

Register access is performed in 16-bit units via the serial peripheral interface. SI is used to specify the register

address (7 bits: A6 to A0) and the read/write setting (1 bit: R/W). During a write operation (R/W = L), data

(8 bits: D7 to D0) should be written to SI, and during a read operation (R/W = H), 8-bit data should be read

from SO. The write data is stored internally at the rising edge of SCK in the last data bit (D7 in the diagram).

The serial peripheral interface sequence during register access is illustrated below.

/CS

SCK

Don't care

Don't care

SI

Don't care A0 A1 A2 A3 A4 A5 A6 R/W D0 D1 D2 D3 D4 D5 D6 D7 Don't care

Write

SO High-Z

operation

(R/W = L)

SI Don't care A0 A1 A2 A3 A4 A5 A6 R/W

Don't care

Read

SO High-Z

D0 D1 D2 D3 D4 D5 D6 D7 High-Z

operation

(R/W = H)

[Note]

• SO is in output mode only during data read operations when /CS = L. Otherwise, high impedance output

is set, so that SCK, SI, and SO can be shared with other devices that have a similar interface.

• Continuous register access is enabled when /CS = L. There is no need to set /CS = H between access

times.

• During a hardware reset (/RST = L), keep /CS to high level (/CS = H)..

• If /CS = H is set during register access, access is stopped. Any write operation that occurs prior to the

rising edge of the 16th SCK signal (SI’s D7 data capture clock) is invalid. SO is set to high impedance.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet YSS950.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| YSS950 | DAP1 Digital Audio Processor | YAMAHA |

| YSS952 | Audio Processing Device APPLICATION MANUAL | YAMAHA |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |