|

|

PDF RX62N Data sheet ( Hoja de datos )

| Número de pieza | RX62N | |

| Descripción | (RX62N / RX621) 100 MHz 32-bit RX MCU | |

| Fabricantes | Renesas Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de RX62N (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Features

Datasheet

RX62N/RX621 Group

RENESAS 32-Bit MCU

R01DS0052EJ0110

Rev.1.10

100 MHz 32-bit RX MCU with FPU, 165 DMIPS, up to 512-Kbyte Flash, Feb 10, 2011

Ethernet, USB 2.0 Full-Speed Host/Function/OTG, CAN, 12-bit ADC, TFT-LCD,

RTC, up to 14 communication channels

Features

■32-bit RX CPU Core

Delivers 165 DMIPS at a maximum operating frequency of

100 MHz

Single Precision 32-bit IEEE-754 Floating Point

Accumulator: 32 × 32 to 64-bit result, one instruction

Mult/Divide Unit, 32 × 32 Multiply in one CPU clock for

multiple instructions

Interrupt response in as few as 5 CPU clock cycles

CISC-Harvard Architecture with 5-stage pipeline

Variable length instructions, ultra compact code

Supports the Memory Protection Unit (MPU)

Background JTAG debug plus high-speed trace

■Low Power Design and Architecture

2.7V to 3.6V operation from a single supply

480 µA/MHz Run Mode with all peripherals on

Deep Software Standby Mode with RTC

Four low power modes

■Main Flash Memory, no Wait-State

100 MHz operation, 10 nsec read cycle

No wait states for read at full CPU speed

256K, 384K, 512K Byte size options

For Instructions or Operands

Programming from USB, SCI, JTAG, user code

■Data Flash Memory

Up to 32K Bytes with 30K Erase Cycles

Background Erase/Program does not stall CPU

■SRAM, no Wait-State

64K or 96K Byte size options

For Operands or Instructions

Back-up retention in Deep Software Standby Mode

■DMA

Four fully programmable internal DMA channels

Two EXDMA channels for external-to-external transfers

Data Transfer Controller (DTC)

■Reset and Supply Management

Power-On Reset (POR) monitor/generator

Low Voltage Detect (LVD) with precision setting

■System Clocking with Clock Monitoring

External crystal, 8 MHz to 14 MHz to Internal PLL

PLL source to system, USB, and Ethernet

Internal 125 kHz LOCO for IWDT

External crystal, 32 kHz for RTC

■Real Time Clock

Full calendar function, BCD format

■Two Independent Watchdog Timers

125-kHz LOCO operation

R01DS0052EJ0110 Rev.1.10

wwwF.DeabtaS1h0e,et240U1.n1et

TFLGA85 7×7mm, 0.65mm pitch

TFLGA145 9×9mm, 0.65mm pitch

LFBGA176 13×13mm, 0.8mm pitch

LQFP100 14×14mm, 0.5mm pitch

LQFP144 20×20mm, 0.5mm pitch

■Up to 14 Communication Interfaces

(2) USB 2.0 Full-Speed interfaces with PHY

Supports Host/Function/OTG

10 endpoints for types: Control, Interrupt, Bulk, Isochronous

(1) Ethernet MAC 10/100 Mbps, Half or Full Duplex

Supported.

Dedicated DMA with 2-Kbyte transmit and receive FIFOs.

RMII or MII interface to external PHY

(1) CAN ISO11898-1, supports 32 mailboxes

(6) SCI channels: Asynchronous, clock sync, smartcard,

and 9-bit modes

(2) I2C interfaces up to 1M bps, SMBus support

(2) RSPI

■External Address Space

Eight CS areas (8 × 16 Mbytes)

128-Mbyte SDRAM area

8-/16-/32-bit bus space selectable for each area

■TFT-LCD up to WQVGA resolution

■Up to 20 Extended Function Timers

(12) 16-bit MTU2

Input capture, Output Compare, PWM output, phase count

mode

(4) 8-bit TMR

(4) 16-bit CMT

■1-MHz ADC units with two combination choices

12-bit × 8 ch. unit with single sample/hold circuit

or (2) 10-bit × 4 ch units each with a sample/hold circuit

AD-converted value addition mode (12-bit A/D converter)

■10-bit DAC, 2 channels

■Up to 128 GPIO

5V tolerant, Open-Drain, Internal Pull-up

■Operation Temp

–40°C to +85°C

Page 1 of 146

1 page

RX62N Group, RX621 Group

1. Overview

Table 1.1 Outline of Specifications (4 / 4)

Classification

Communication

function

Module/Function

I2C bus interfaces

CAN module

Serial peripheral

interfaces

12-bit A/D converter

10-bit A/D converter

D/A converter

CRC calculator

Description

· 2 channels (100-pin version: 1 channel)

· Communications formats

I2C bus format/SMBus format

Master/slave selectable (For multi-master operation)

· 1 channel

· 32 mailboxes

· 2 channels

· RSPI transfer facility

Using the MOSI (master out, slave in), MISO (master in, slave out), SSL (slave select),

and RSPI clock (RSPCK) signals enables serial transfer through SPI operation (four

lines) or clock-synchronous operation (three lines)

Capable of handling serial transfer as a master or slave

· Data formats

Switching between MSB first and LSB first

The number of bits in each transfer can be changed to any number of bits from 8 to 16, or

to 20, 24, or 32 bits.

128-bit buffers for transmission and reception

Up to four frames can be transmitted or received in a single transfer operation (with each

frame having up to 32 bits)

· Buffered structure

· Double buffers for both transmission and reception

· 12 bits x 1 unit (1 unit x 8 channels) or 10 bits x 2 units (2 units x 4 channels);

12- and 10-bit A/D converters can be exclusively used.

· 10- or 12-bit resolution

· Conversion time: 1.0 s per channel (in operation with PCLK at 50 MHz)

· Two operating modes

Single mode

Scan mode (one-cycle scan mode or continuous scan mode)

· Sample-and-hold function

· Three ways to start A/D conversion

Conversion can be started by software, a conversion start trigger from a timer (MTU or

TMR), or an external trigger signal.

· Self-diagnostic functions

· 2 channels (1 channel for 100-pin products)

· 10-bit resolution

· Output voltage: 0 V to VREFH

· CRC code generation for arbitrary amounts of data in 8-bit units

· Select any of three generating polynomials:

X8 + X2 + X + 1, X16 + X15 + X2 + 1, or X16 + X12 + X5 + 1.

· Generation of CRC codes for use with LSB-first or MSB-first communications is

selectable.

Operating frequency

8 to 100 MHz

Power supply voltage

VCC = PLLVCC = AVCC = 2.7 to 3.6V, VREFH = 2.7 to AVCC

Operating temperature

40 to +85C

Package

176-pin LFBGA (PLBG0176GA-A), 145-pin TFLGA (PTLG0145JB-A),

144-pin LQFP (PLQP0144KA-A), 100-pin LQFP (PLQP0100KB-A)*2

85-pin TFLGA (PTLG0085JA-A)*2, * 3

Note 1. As for the MPU, contact your Renesas sales agency.

Note 2. For products in the 100-pin LQFP and 85-pin TFLGA, BCLK is synchronized with 8 to 25 MHz.

Note 3. MSB-first order is only available in the smart-card interface mode.

R01DS0052EJ0110 Rev.1.10

Feb 10, 2011

Page 5 of 146

5 Page

RX62N Group, RX621 Group

1. Overview

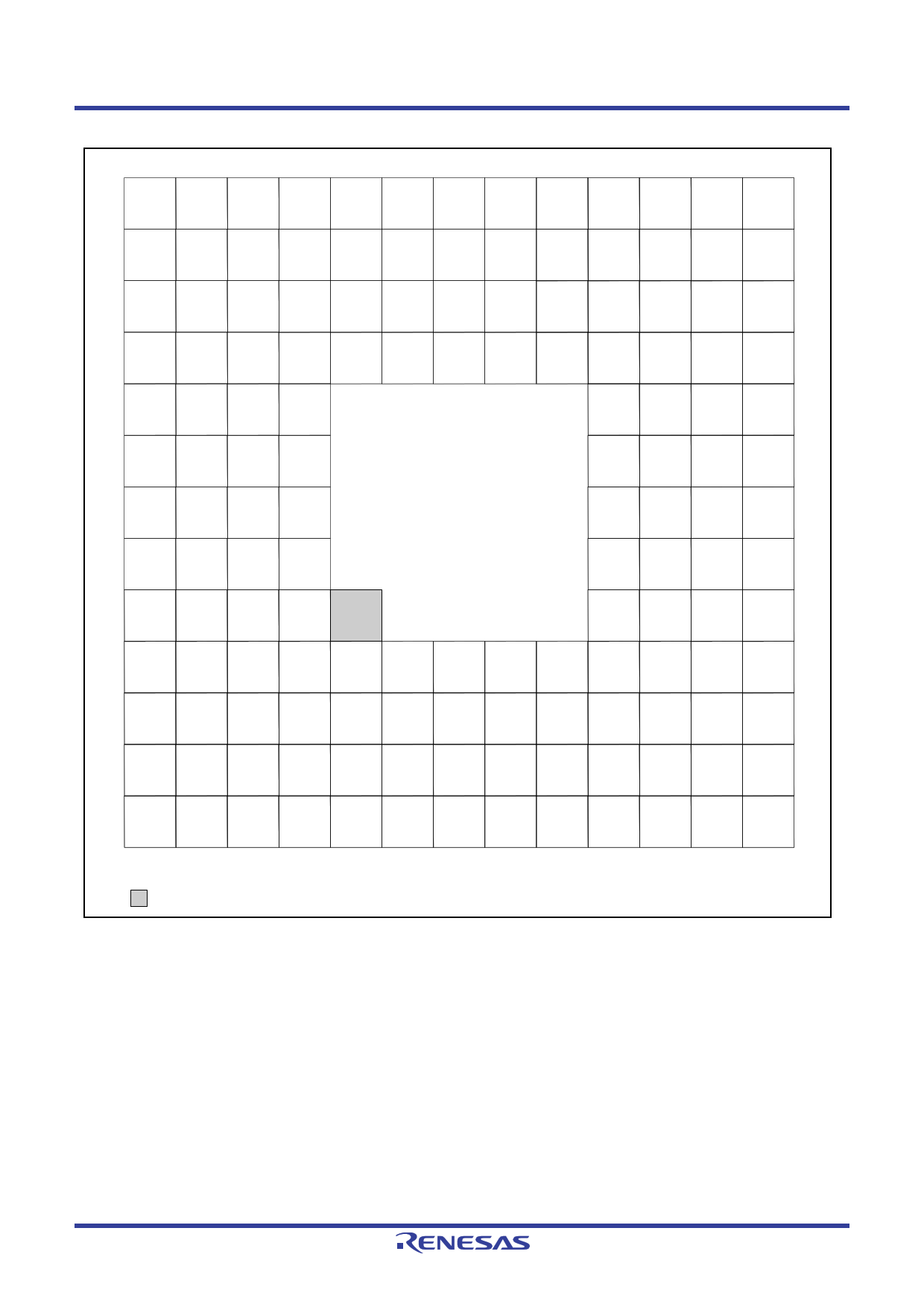

A BCD E FGH J K LMN

13 P64 PE4 P70 PE6 P66 PA2 PA4 PA7 P72 PB3 PB6 VSS P74 13

12 P62 PE1 PE3 PE7 PA0 VCC PA6 PB1 PB5 PC0 VCC PC1 P76 12

11 P60 PE2 PE5 VCC P67 PA3 PA5 P71 PB4 P73 P75 PC2 PC4 11

10 PD6 PE0 P63 VSS P65 PA1 VSS PB0 PB2 PB7 P77 P80 PC5 10

9 PD3 VSS P61 VCC

PC3 P81 PC6 VCC 9

8 PD0 PD5 PD7 PD4

7 P91 PD1 PD2 P93

6 P47 P90 P92 VSS

RX62N Group

RX621 Group

PTLG0145JB-A

(145-pin TFLGA)

(Upper perspective view)

5 P44 P45 P46 VCC NC

P82 P83 P50 P51 8

PC7 P52 P55 P54 7

VSS

P56

VSS_ USB0_

USB

DP 6

P53

VCC_

USB

P14

USB0_

DM 5

4 P42 P40 P41 P43 BSCANP MDE MD0 RES# P32 P26 P12 P15 P13 4

3 VREFL VREFH VSS

P02

P00 WDTOVF# MD1

VCC

P35

P31

P17 PLLVCC PLLVSS 3

2 AVCC P07

P05

VCC

VSS XCOUT VSS

P34

P27

P24

P22

P20

P16 2

1 AVSS P03 P01 EMLE VCL XCIN XTAL EXTAL P33 P30 P25 P23 P21 1

A BCD E FGH J K LMN

: NC pin

Figure 1.4 Pin Assignment of the 145-Pin TFLGA

R01DS0052EJ0110 Rev.1.10

Feb 10, 2011

Page 11 of 146

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet RX62N.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| RX621 | (RX62N / RX621) 100 MHz 32-bit RX MCU | Renesas Technology |

| RX62G | 100-MHz 32-bit RX MCUs | Renesas |

| RX62N | (RX62N / RX621) 100 MHz 32-bit RX MCU | Renesas Technology |

| RX62T | 100-MHz 32-bit RX MCUs | Renesas |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |