|

|

PDF EM68916DVAA Data sheet ( Hoja de datos )

| Número de pieza | EM68916DVAA | |

| Descripción | 8M x 16 Mobile DDR Synchronous DRAM | |

| Fabricantes | Etron Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EM68916DVAA (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet.co.kr

EtronTech

EM68916DVAA

8M x 16 Mobile DDR Synchronous DRAM (SDRAM)

Etron Confidential

Advanced (Rev. 1.0 Apr. /2009)

Features

• Fast clock rate: 166/133 MHz

• Differential Clock CK & CK

• Bi-directional DQS

• Four internal banks, 2M x 16-bit for each bank

• Edge-aligned with read data, centered in write

data

• Programmable Mode and Extended Mode Registers

- CAS Latency: 2, or 3

- Burst length: 2, 4, or 8

- Burst Type: Sequential & Interleaved

- PASR (Partial Array Self Refresh)

- Auto TCSR (Temperature Compensated Self

Refresh)

- DS (Drive Strength)

• Individual byte writes mask control

• DM Write Latency = 0

• Precharge Standby Current = 100 µA

• Self Refresh Current = 200 µA

• Deep power-down Current = 10 µA max. at 85

• Auto Refresh and Self Refresh

• 4096 refresh cycles / 64ms

• No DLL (Delay Lock Loop), to reduce power; CK to

DQS is not synchronized.

• Power supplies: VDD & VDDQ = +1.8V+0.15V/-0.1V

• Interface: LVCMOS

• Ambient Temperature TA = -25 ~ 85 ,

• 60-ball 8mm x 10mm VFBGA package

- Pb free and Halogen free

Table 1. Ordering Information

Part Number

Clock

Frequency

Data Rate

IDD6 Package

EM68916DVAA-6H 166MHz 333Mbps/pin 200 µA VFBGA

EM68916DVAA-75H 133MHz 266Mbps/pin 200 µA VFBGA

VA: indicates VFBGA package

A: indicates Generation Code

H: indicates Pb and Halogen Free for VFBGA Package

Figure 1. Ball Assignment (Top View)

123

A VSS

DQ15

VSSQ

B VDDQ

DQ13

DQ14

C VSSQ

DQ11

DQ12

D VDDQ

DQ9

DQ10

E VSSQ

UDQS

F VSS UDM

G CKE

CK

H A9

A11

DQ8

NC

CK

NC

J A6

K VSS

A7

A4

A8

A5

7

VDDQ

8

DQ0

9

VDD

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

LDQS

VDDQ

NC

LDM

VDD

WE

CAS

RAS

CS

BA0

BA1

A10/AP

A0

A1

A2 A3 VDD

Overview

The EM68916D is 134,217,728 bits of double data

rate synchronous DRAM organized as 4 banks of

2,097,152 words by 16 bits. The synchronous

operation with Data Strobe allows extremely high

performance. EM68916D is applied to reduce

leakage and refresh currents while achieving very

high speed. I/O transactions are possible on both

edges of the clock. The ranges of operating

frequencies, programmable burst length and

programmable latencies allow the device to be

useful for a variety of high performance memory

system applications.

Etron Technology, Inc.

No. 6, Technology Rd. V, Hsinchu Science Park, Hsinchu, Taiwan 30078, R.O.C.

TEL: (886)-3-5782345 FAX: (886)-3-5778671

Etron Technology, Inc. reserves the right to change products or specification without notice.

Datasheet pdf - http://www.DataSheet4U.net/

1 page

www.DataSheet.co.kr

EtronTech

EM68916DVAA

Operation Mode

Fully synchronous operations are performed to latch the commands at the positive edges of CK. Table 3 shows

the truth table for the operation commands.

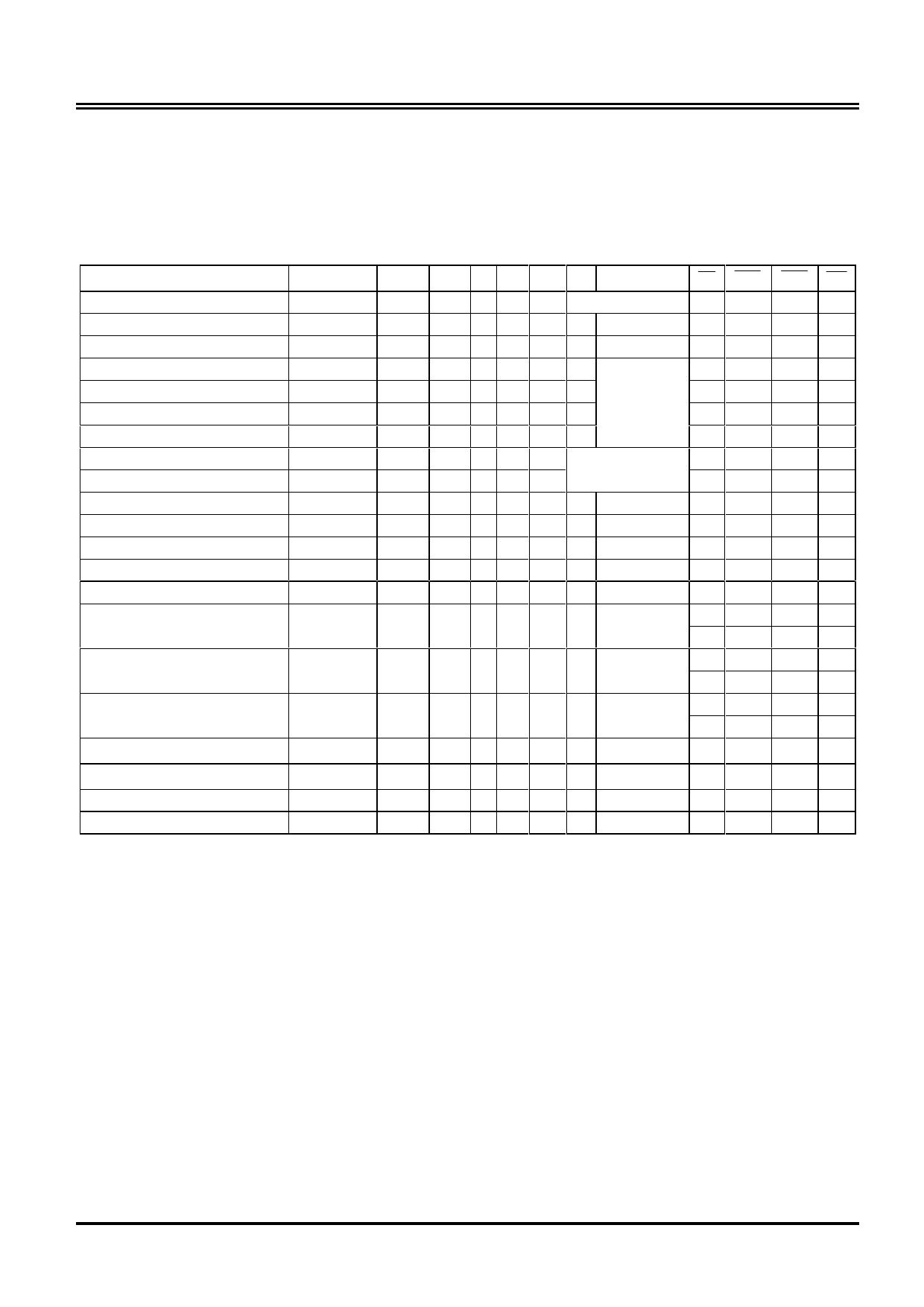

Table 3. Truth Table (Note (1), (2))

Command

State CKEn-1 CKEn DM BA1 BA0 A10 A11, A9-0 CS RAS CAS WE

BankActivate

Idle(3)

H X X V V Row Address L L H H

BankPrecharge

Any H X X V V L X

LL HL

PrechargeAll

Any H X X X X H X

LL HL

Write

Write and AutoPrecharge

Read

Read and Autoprecharge

Active(3) H X V V V L

LH L L

Active(3)

H

X VV V H

Column

Address

L

H

LL

Active(3) H X X V V L A0~A8 L H L H

Active(3) H X X V V H

LH LH

Mode Register Set

Extended Mode Register Set

Idle

Idle

H X XL L

H X XH L

OP code

LL

LL

LL

LL

No-Operation

Any H X X X X X X

LH HH

Device Deselect

Any H X X X X X X H X X X

Burst Stop

Active(4) H X X X X X

X

LH HL

AutoRefresh

Idle H H X X X X X

LL LH

SelfRefresh Entry

Idle H L X X X X X

LL LH

SelfRefresh Exit

Idle

(Self Refresh)

L

H XX X X

X

HX

LH

XX

HH

Power Down Mode Entry

Idle/Active(5

)

H

L XX X X

X

HX

LH

XX

HH

Power Down Mode Exit

Any

(Power Down)

L

H XX X X

X

HX

LH

XX

HH

Deep Power Down Entry

Any H L X X X X X

LH HL

Deep Power Down Exit

Any L H X X X X X H X X X

Data Write Enable

Active

H X LX X X

X

XX XX

Data Mask Disable

Active

H X HX X X

X

XX

Note: 1. V = Valid data, X = Don't Care, L = Low level, H = High level

2. CKEn signal is input level when commands are provided.

CKEn-1 signal is input level one clock cycle before the commands are provided.

3. These are states of bank designated by BA0, BA1signals.

4. Read burst stop with BST command for all burst types.

5. Power Down Mode can not enter in the burst operation.

When this command is asserted in the burst cycle, device state is clock suspend mode.

XX

Etron Confidential

5

Rev. 1.0

Apr. 2009

Datasheet pdf - http://www.DataSheet4U.net/

5 Page

www.DataSheet.co.kr

EtronTech

EM68916DVAA

Write Interrupted by Write

A Burst Write can be interrupted by the new Write command before completion of the previous Burst Write,

with the only restriction being that the interval that separates the commands must be at least one clock cycle.

When the previous burst is interrupted, the remaining addresses are overridden by the new addresses and

the new data will be written into the device until the programmed Burst Length is satisfied.

Write Interrupted by Read & DM

A Burst Write can be interrupted by a Read command to any bank. The DQ must be in the high impedance

state at least one clock cycle before the interrupting read data appears on the outputs to avoid data

contention. When the Read command is to be asserted, any residual data from the Burst Write sequence

must be masked by DM. The delay from the last data to the Read command (tWTR) is required to avoid data

contention inside the DRAM. Data presented on the DQ pins before the Read command is initiated will

actually be written to the memory. A Read command interrupting a write sequence can not be issued at the

next clock edge following the Write command.

Write Interrupted by Precharge & DM

A Burst Write can be interrupted by a Precharge of the same bank before completion of the previous burst. A

write recovery time (tWR) is required from the last data to the Precharge command. When the Precharge

command is asserted, any residual data from the Burst Write cycle must be masked by DM.

z Burst Stop Command

The Burst Stop command is initiated by having RAS and CAS High with CS and WE Low at the rising edge

of the clock only. The Burst Stop command has the fewest restrictions, making it the easiest method to use

when terminating a burst operation before it has been completed. When the Burst Stop command is issued

during a Burst Read cycle, both the data and DQS (Data Strobe) go to a high impedance state after a delay

which is equal to the CAS latency set in the Mode Register. The Burst Stop command, however, is not

supported during a Burst Write operation.

z DM Masking Function

The DDR SDRAM has a Data Mask function that can be used in conjunction with the data write cycle only, not

the read cycle. When the Data Mask is activated (DM High) during a write operation, the write data is masked

immediately (DM to Data Mask latency is zero). DM must be issued at the rising edge or the falling edge of

Data Strobe instead of at a clock edge.

z Auto Precharge Operation

Auto Precharge is a feature which performs the same individual bank precharge function as described above,

but without requiring an explicit command. This is accomplished by using A10 (A10 = High), to enable Auto

Precharge in conjunction with a specific READ or WRITE command. A precharge of the bank / row that is

addressed with the READ or WRITE command is automatically performed upon completion of the read or

write burst. Auto Precharge is non persistent in that it is either enabled or disabled for each individual READ

or WRITE command. Auto Precharge ensures that a precharge is initiated at the earliest valid stage within a

burst. The user must not issue another command to the same bank until the precharging time (tRP) is

completed. When the Auto Precharge command is activated, the active bank automatically begins to

precharge at the earliest possible moment during a read or write cycle after tRAS (min) is satisfied.

z Precharge Command

The Precharge command is issued when CS , RAS , and WE are Low and CAS is High at the rising edge of

the clock (CK). The Precharge command can be used to precharge any bank individually or all banks

simultaneously. The Bank Select addresses (BA0, BA1) are used to define which bank is precharged when

the command is initiated. For a write cycle, tWR (min) must be satisfied from the start of the last Burst Write

cycle until the Precharge command can be issued. After tRP from the precharge, an Active command to the

same bank can be initiated.

Etron Confidential

11

Rev. 1.0

Apr. 2009

Datasheet pdf - http://www.DataSheet4U.net/

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EM68916DVAA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EM68916DVAA | 8M x 16 Mobile DDR Synchronous DRAM | Etron Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |