|

|

PDF QD14TL01 Data sheet ( Hoja de datos )

| Número de pieza | QD14TL01 | |

| Descripción | TFT LCD Module | |

| Fabricantes | Quanta | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de QD14TL01 (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

Preliminary

Spec.

Quanta Display Inc.

SPECIFICATION

Doc No. QD14TL0103

Doc. REV.: 02

Issue Date: 4/08/2005

With RoHS

Compliant

Specification for TFT LCD Module

Model No.

QD14TL01 Rev.:03

www.DataSheet.co.kr

Approved By

Quanta Display Inc.

Datasheet pdf - http://www.DataSheet4U.net/

1 page

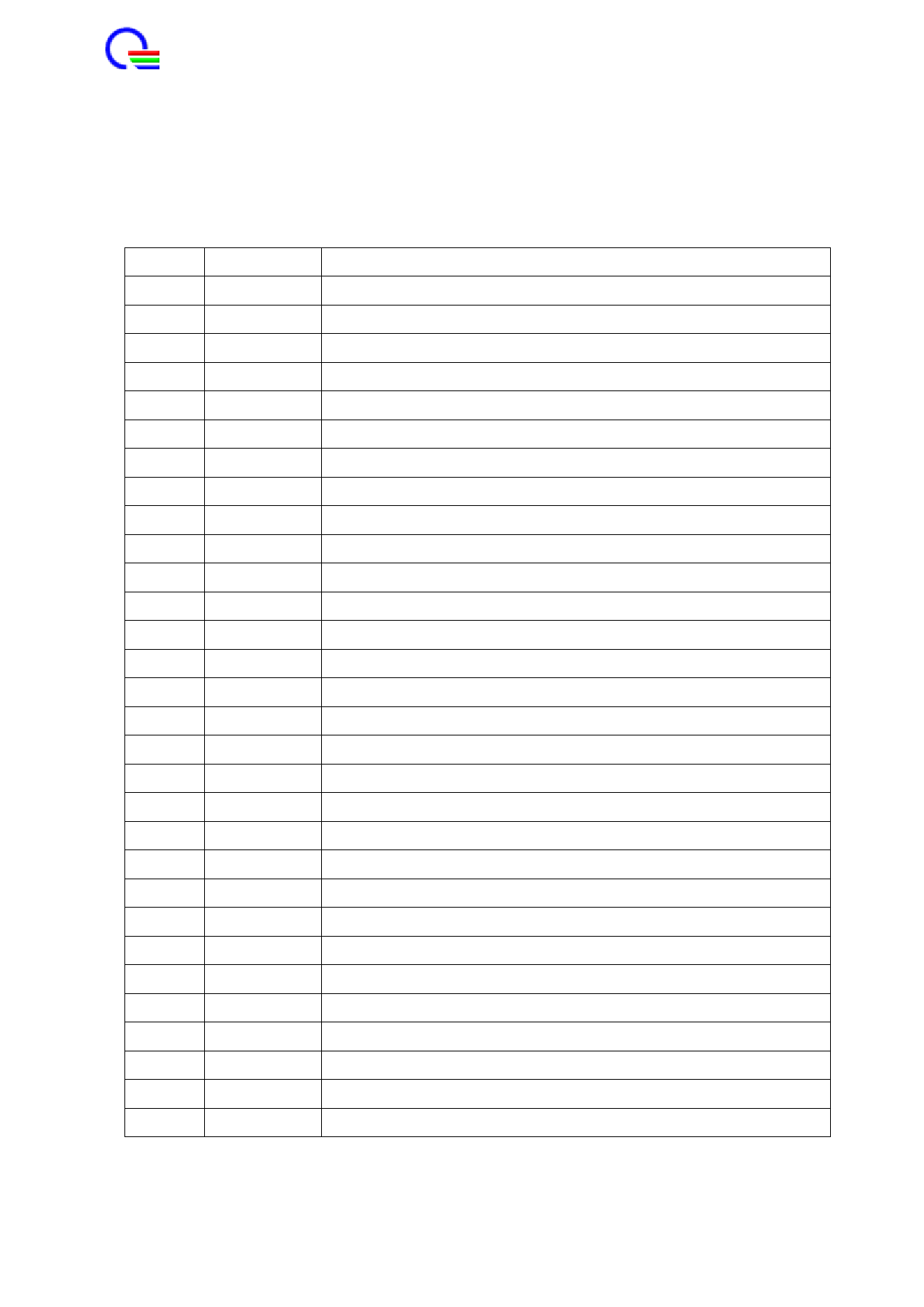

4. Input Connectors

4-1 Signal Interface Connector

CN1 (1 channel, LVDS signals – NSC/Ti standard and +3.3V DC power supply)

Using connector: FI-XB30Sx-HFxx/FI-X30Sx-HFxx/equivalent (JAE)

Interface Cable Pin Assignments

PIN NO SYMBOL

FUNCTION

1 VSS

Ground

2 VDD

Power Supply, 3.3 V (typical)

3 VDD

Power Supply, 3.3 V (typical)

4

V EEDID

DDC 3.3V power

5 NC

Reserved for supplier test point

6 Clk EEDID DDC Clock

7 DATA EEDID DDC Data

8 Rin0-

- LVDS differential data input (R0-R5, G0) (odd pixels)

9 Rin0+ + LVDS differential data input (R0-R5, G0) (odd pixels)

10 VSS

Ground

11 Rin1-

- LVDS differential data input (G1-G5, B0-B1) (odd pixels)

12 Rin1+

+ LVDS differential data input (G1-G5, B0-B1) (odd pixels)

13 VSS

Ground

14 Rin2-

15 Rin2+

- LVDS differential data input (B2-B5, HS, VS, DE) (odd pixels)

www.DataSheet.co.kr

+ LVDS differential data input (B2-B5, HS, VS, DE) (odd pixels)

16 VSS

Ground

17 ClkIN-

- LVDS differential clock input (odd pixels)

18 ClkIN+ + LVDS differential clock input (odd pixels)

19 VSS

Ground

20 NC

No connect

21 NC

No connect

22 VSS

Ground

23 NC

No connect

24 NC

No connect

25 VSS

Ground

26 NC

No connect

27 NC

No connect

28 VSS

Ground

29 NC

No connect

30 NC

No connect

[Note 1] Relation between LVDS signals and actual data shows below section (4-2).

[Note 2] The shielding case is connected with signal GND.

Datasheet pdf - http://www.DataSheet4U.net/

5 Page

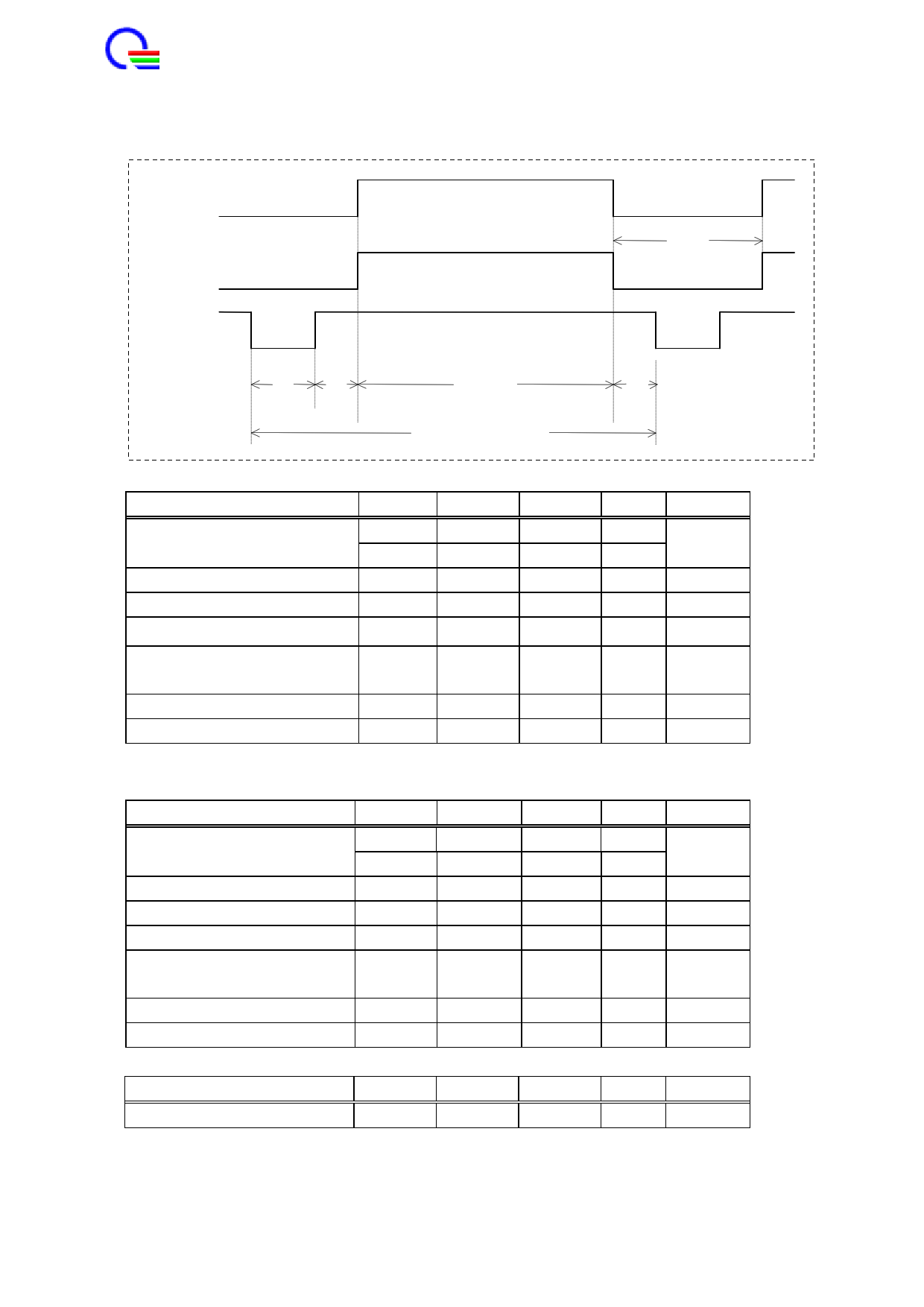

7. Timing characteristics of LCD module input signals

7-1. Timing characteristics

(This is specified at digital outputs of LVDS driver.)

Data

ENAB

Sync

Vertical

Item symbol

Vsync cycle (TVA)

Blanking period(TVB)

Sync pulse width (TVC)

Back porch (TVD)

Sync pulse width + Back

porch (TVC+TVD)

Active display area (TVE)

Front porch (TVF)

Min.

808

8

2

5

7

800

1

Typ.

16.667

816

16

4

8

12

www.DataSheet.co.kr

800

4

Max.

850

--

800

Unit Remark

ms Negative

line

line

line

line

line

line

line

( Horizontal )

Item symbol

Min.

Typ.

Max. Unit Remark

Hsync cycle (THA)

Blanking period (THB)

Sync pulse width (THC)

Back porch (THD)

Sync pulse width + Back

porch (THC +THD)

Active display area (THE)

Front porch (THF)

Clock

Item

1380

100

16

68

84

1280

16

Min.

20.44

1408

128

32

75

107

1280

21

Typ.

1428

--

s

clock

clock

clock

clock

clock

Negative

1280

clock

clock

Max. Unit Remark

Frequency

67 68.9 72 MHz [Note1]

[Note] In case of lower frequency, the deterioration of display quality, flicker etc., may be

occurred.

Datasheet pdf - http://www.DataSheet4U.net/

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet QD14TL01.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| QD14TL01 | TFT LCD Module | Quanta |

| QD14TL02 | TFT LCD Module | Quanta |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |