|

|

PDF ATA5728 Data sheet ( Hoja de datos )

| Número de pieza | ATA5728 | |

| Descripción | (ATA5723 - ATA5728) UHF ASK/FSK Receiver | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ATA5728 (archivo pdf) en la parte inferior de esta página. Total 46 Páginas | ||

|

No Preview Available !

Features

• Frequency Receiving Range of (3 Versions)

– f0 = 312.5 MHz to 317.5 MHz or

– f0 = 431.5 MHz to 436.5 MHz or

– f0 = 868 MHz to 870 MHz

• 30 dB Image Rejection

• Receiving Bandwidth

– BIF = 300 kHz for 315 MHz/433 MHz Version

– BIF = 600 kHz for 868 MHz Version

• Fully Integrated LC-VCO and PLL Loop Filter

• Very High Sensitivity with Power Matched LNA

– ATA5723/ATA5724:

–107 dBm, FSK, BR_0 (1.0 kBit/s to 1.8 kBit/s), Manchester, BER 10E-3

–113 dBm, ASK, BR_0 (1.0 kBit/s to 1.8 kBit/s), Manchester, BER 10E-3

– ATA5728:

–105 dBm, FSK, BR_0 (1.0 kBit/s to 1.8 kBit/s), Manchester, BER 10E-3

–111 dBm, ASK, BR_0 (1.0 kBit/s to 1.8 kBit/s), Manchester, BER 10E-3

• High System IIP3

– –18 dBm at 868 MHz

– –23 dBm at 433 MHz

– –24 dBm at 315 MHz

• System 1-dB Compression Point

– –27.7 dBm at 868 MHz

– –32.7 dBm at 433 MHz

– –33.7 dBm at 315 MHz

• High Large-signal Capability at GSM Band (Blocking –33 dBm at +10 MHz,

IIP3 = –24 dBm at +20 MHz)

• Logarithmic RSSI Output

• XTO Start-up with Negative Resistor of 1.5 kΩ

• 5V to 20V Automotive Compatible Data Interface

• Data Clock Available for Manchester and Bi-phase-coded Signals

• Programmable Digital Noise Suppression

• Low Power Consumption Due to Configurable Polling

• Temperature Range –40°C to +105°C

• ESD Protection 2 kV HBM, All Pins

• Communication to Microcontroller Possible using a Single Bi-directional Data Line

• Low-cost Solution Due to High Integration Level with Minimum External Circuitry

Requirements

• Supply Voltage Range 4.5V to 5.5V

Benefits

• Low BOM List Due to High Integration

• Use of Low-cost 13 MHz Crystal

• Lowest Average Current Consumption for Application Due to Self Polling Feature

• Reuse of ATA5743 Software

• World-wide Coverage with One PCB Due to 3 Versions are Pin Compatible

UHF ASK/FSK

Receiver

ATA5723

ATA5724

ATA5728

9106E–RKE–07/08

Free Datasheet http://www.datasheet4u.com/

1 page

ATA5723/ATA5724/ATA5728

3. RF Front-end

The RF front-end of the receiver is a low-IF heterodyne configuration that converts the input sig-

nal into about 1 MHz IF signal with a typical image rejection of 30 dB. According to Figure Figure

1-2 on page 3 the front-end consists of an LNA (Low Noise Amplifier), LO (Local Oscillator), I/Q

mixer, polyphase low-pass filter and an IF amplifier.

The PLL generates the drive frequency fLO for the mixer using a fully integrated synthesizer with

integrated low noise LC-VCO (Voltage Controlled Oscillator) and PLL-loop filter. The XTO (crys-

tal oscillator) generates the reference frequency fREF = fXTO/2 (868 MHz and 433 MHz versions)

or fREF = fXTO/3 (315 MHz version). The integrated LC-VCO generates two or four times the

mixer drive frequency fVCO. The I/Q signals for the mixer are generated with a divide by two or

four circuit (fLO = fVCO/2 for 868 MHz version, fLO = fVCO/4 for 433 MHz and 315 MHz versions).

fVCO is divided by a factor of 128 or 64 and feeds into a phase frequency detector and is com-

pared with fREF. The output of the phase frequency detector is fed into an integrated loop filter

and thereby generates the control voltage for the VCO. If fLO is determined, fXTO can be calcu-

lated using the following formula:

fREF = fLO/128 for 868 MHz band, fREF = fLO/64 for 433 MHz bands, fREF = fLO/64 for 315 MHz

bands.

The XTO is a two-pin oscillator that operates at the series resonance of the quartz crystal with

high current but low voltage signal, so that there is only a small voltage at the crystal oscillator

frequency at pins XTAL1 and XTAL2. According to Figure 3-1, the crystal should be connected

to GND with two capacitors CL1 and CL2 from XTAL1 and XTAL2 respectively. The value of

these capacitors are recommended by the crystal supplier. Due to an inductive impedance at

steady state oscillation and some PCB parasitics, a lower value of CL1 and CL2 is normally

necessary.

The value of CLx should be optimized for the individual board layout to achieve the exact value of

fXTO and hence of fLO. (The best way is to use a crystal with known load resonance frequency to

find the right value for this capacitor.) When designing the system in terms of receiving band-

width and local oscillator accuracy, the accuracy of the crystal and the XTO must be considered.

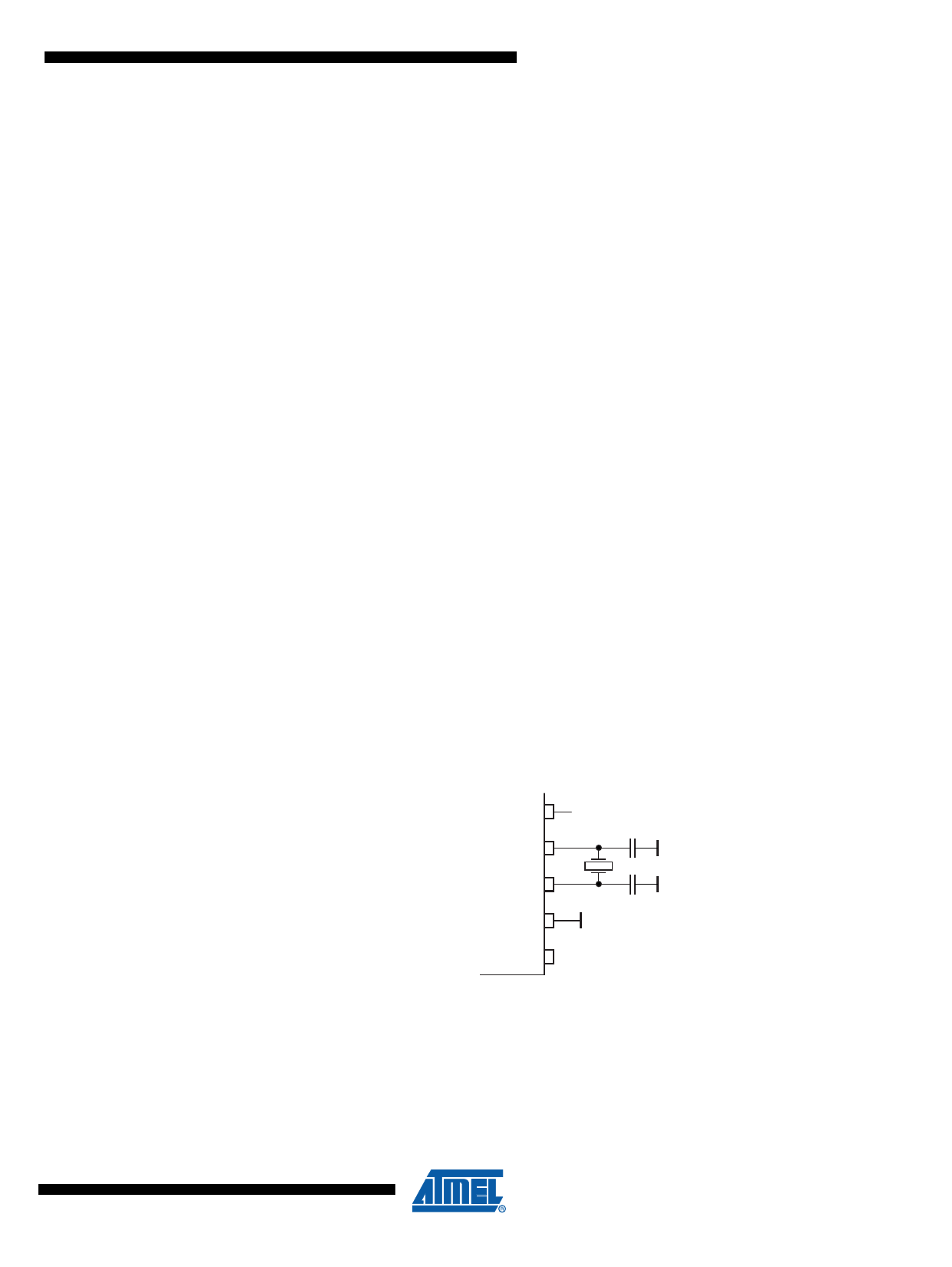

Figure 3-1. XTO Peripherals

VS

DVCC

XTAL2

CL2

XTAL1

TEST3

CL1

TEST2

The nominal frequency fLO is determined by the RF input frequency fRF and the IF frequency fIF

using the following formula (low-side injection):

fLO = fRF – fIF

9106E–RKE–07/08

5

Free Datasheet http://www.datasheet4u.com/

5 Page

ATA5723/ATA5724/ATA5728

The clock cycle of some function blocks depends on the selected baud-rate range (BR_Range),

which is defined in the OPMODE register. This clock cycle TXClk is defined by the following

formulas:

BR_Range =

BR_Range0:

BR_Range1:

BR_Range2:

BR_Range3:

TXClk = 8 × TClk

TXClk = 4 × TClk

TXClk = 2 × TClk

TXClk = 1 × TClk

8. Polling Mode

According to Figure 8-1 on page 12, the receiver stays in polling mode in a continuous cycle of

three different modes. In sleep mode the signal processing circuitry is disabled for the time

period TSleep while consuming low current of IS = ISoff. During the start-up period, TStartup, all sig-

nal processing circuits are enabled and settled. In the following bit-check mode, the incoming

data stream is analyzed bit-by-bit and compared with a valid transmitter signal. If no valid signal

is present, the receiver is set back to sleep mode after the period TBit-check. This period varies

according to each check as it is a statistical process. An average value for TBitcheck is given in the

electrical characteristics. During TStartup and TBit-check, the current consumption is IS = ISon. The

condition of the receiver is indicated on pin IC_ACTIVE. The average current consumption in

polling mode is dependent on the duty cycle of the active mode and can be calculated as:

ISpoll

=

I--S----o--f--f--×------T----S---l-e---e---p----+-----I--S---o---n----×------(--T----S---t-a---r--t-u---p----+-----T----B---i-t----c--h---e---c--k---)

TSleep + TStartup + TBit-check

During TSleep and TStartup, the receiver is not sensitive to a transmitter signal. To guarantee the

reception of a transmitted command, the transmitter must start the telegram with an adequate

preburst. The required length of the preburst depends on the polling parameters TSleep, TStartup,

TBit-check and the start-up time of a connected microcontroller, TStart_microcontroller. Thus, TBit-check

depends on the actual bit rate and the number of bits (NBit-check) to be tested.

The following formula indicates how to calculate the preburst length.

TPreburst ≥ TSleep + TStartup + TBit-check + TStart_microcontroller

8.1 Sleep Mode

The length of period TSleep is defined by the 5-bit word Sleep of the OPMODE register, the exten-

sion factor XSleep (according to Table 11-8 on page 27), and the basic clock cycle TClk. It is

calculated to be:

TSleep = Sleep × XSleep × 1024 × TClk

The maximum value of TSleep is about 60 ms if XSleep is set to 1. The time resolution is about

2 ms in that case. The sleep time can be extended to almost half a second by setting XSleep to 8.

XSleep can be set to 8 by bit XSleepStd to “1”.

Setting the configuration word Sleep to its maximal value puts the receiver into a permanent

sleep mode. The receiver remains in this state until another value for Sleep is programmed into

the OPMODE register. This is particularily useful when several devices share a single data line.

(It can also be used for microcontroller polling: using pin POLLING/_ON, the receiver can be

switched on and off.)

9106E–RKE–07/08

11

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 46 Páginas | |

| PDF Descargar | [ Datasheet ATA5728.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ATA5723 | (ATA5723 - ATA5728) UHF ASK/FSK Receiver | ATMEL Corporation |

| ATA5724 | (ATA5723 - ATA5728) UHF ASK/FSK Receiver | ATMEL Corporation |

| ATA5728 | (ATA5723 - ATA5728) UHF ASK/FSK Receiver | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |