|

|

PDF HIP6028EVAL1 Data sheet ( Hoja de datos )

| Número de pieza | HIP6028EVAL1 | |

| Descripción | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HIP6028EVAL1 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

Data Sheet

HIP6028

May 1998

File Number 4630

Advanced PWM and Dual Linear Power

Control with Integrated ACPI Support

Interface

The HIP6028 provides the power control and protection for

three output voltages in high-performance microprocessor

and computer applications. The IC integrates a PWM

controller, a linear regulator and a linear controller as well as

the monitoring and protection functions into a single

package. The PWM controller regulates the microprocessor

core voltage with a synchronous-rectified buck converter.

The linear controller regulates power for the GTL bus and

the linear regulator provides power for the clock driver circuit.

The HIP6028 includes an Intel-compatible, TTL 5-input

digital-to-analog converter (DAC) that adjusts the core PWM

output voltage from 2.1VDC to 3.5VDC in 0.1V increments

and from 1.3VDC to 2.05VDC in 0.05V steps. The precision

reference and voltage-mode control provide ±1% static

regulation. The linear regulator uses an internal pass device

to provide a fixed 2.5V ±2.5%. The linear controller drives an

external N-channel MOSFET to provide a fixed 1.5V ±2.5%.

The HIP6028 monitors all the output voltages. A single

Power Good signal is issued when the core is within ±10% of

the DAC setting and the other levels are above their under-

voltage levels. Additional built-in over-voltage protection for

the core output uses the lower MOSFET to prevent output

voltages above 115% of the DAC setting. The PWM over-

current function monitors the output current by using the

voltage drop across the upper MOSFET’s rDS(ON),

eliminating the need for a current sensing resistor.

The HIP6028 offers integrated ACPI S3 shutdown state

support. Through the SD1&3 pin, the microprocessor core

and GTL bus supplies can be shut down when entering

power-saving standby operation mode.

Ordering Information

PART NUMBER

TEMP.

RANGE

(oC)

PACKAGE

HIP6028CB

0 to 70 24 Ld SOIC

HIP6028EVAL1 Evaluation Board

PKG. NO.

M24.3

Features

• Provides 3 Regulated Voltages

- Microprocessor Core, Clock and GTL Power

• Integrated ACPI S3-State Shutdown Support

• Drives Low Cost Transistors

- PWM Controller Drives N-MOSFETs

- Linear Controller Compatible with Both MOSFETs and

NPN Bipolar Transistors

• Operates from +3.3V, +5V and +12V Inputs

• Simple Control Design

- Single-Loop Voltage-Mode PWM Control

- Fixed 1.5V GTL Output Voltage

- Fixed 2.5V Clock Output Voltage

• Fast Transient Response

- High-Bandwidth Error Amplifier

- Full 0% to 100% Duty Ratio

• Excellent Output Voltage Regulation

- Core PWM Output: ±1% Over Temperature

- Other Outputs: ±2.5% Over Temperature

• TTL-compatible 5-Bit Digital-to-Analog Core Output

Voltage Selection

- Wide Range . . . . . . . . . . . . . . . . . . . 1.3VDC to 3.5VDC

• Power-Good Output Voltage Monitor

• Microprocessor Core Voltage Protection Against Shorted

MOSFET

• Over-Voltage and Over-Current Fault Monitors

- Does Not Require Extra Current Sensing Element,

Uses MOSFET’s rDS(ON)

• Small Converter Size

- Constant Frequency Operation; 200kHz Free-Running

Oscillator; Programmable from 50kHz to 1MHz

Applications

• Full Motherboard Power Regulation for Computers

• Low-Voltage Distributed Power Supplies

Pinout

HIP6028 (SOIC)

TOP VIEW

VCC 1

VID4 2

VID3 3

VID2 4

VID1 5

VID0 6

PGOOD 7

FAULT 8

SS 9

RT 10

SD1&3 11

VIN2 12

24 UGATE

23 PHASE

22 LGATE

21 PGND

20 OCSET

19 VSEN1

18 FB

17 COMP

16 VSEN3

15 DRIVE3

14 GND

13 VOUT2

2-311

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

1 page

HIP6028

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. Refer to Figures 1, 2 and 3 (Continued)

PARAMETER

SYMBOL

TEST CONDITIONS

MIN TYP MAX UNITS

Slew Rate

SR COMP = 10pF

- 6 - V/µs

PWM CONTROLLER GATE DRIVER

Upper Drive Source

Upper Drive Sink

Lower Drive Source

Lower Drive Sink

PROTECTION AND CONTROL

IUGATE

RUGATE

ILGATE

RLGATE

VCC = 12V, VUGATE (or VGATE2) = 6V

VUGATE-PHASE = 1V

VCC = 12V, VLGATE = 1V

VLGATE = 1V

-1-

- 1.7 3.5

-1-

- 1.4 3.0

A

Ω

A

Ω

VOUT1 Over-Voltage Trip

FAULT Sourcing Current

OCSET Current Source

Soft-Start Current

VOUT1 and VOUT3 Disable Low Voltage

VOUT1 and VOUT3 Disable High Voltage

POWER GOOD

IOVP

IOCSET

ISS

VSEN1 Rising

VFAULT = 10V

VOCSET = 4.5VDC

112 115 118

10 14

-

170 200 230

- 11 -

- - 0.8

2.0 -

-

%

mA

µA

µA

V

V

VOUT1 Upper Threshold

VOUT1 Under Voltage

VOUT1 Hysteresis (VSEN1 / DACOUT)

PGOOD Voltage Low

VSEN1 Rising

VSEN1 Rising

Upper/Lower Threshold

VPGOOD IPGOOD = -4mA

108 - 110

92 - 94

-2-

- - 0.5

%

%

%

V

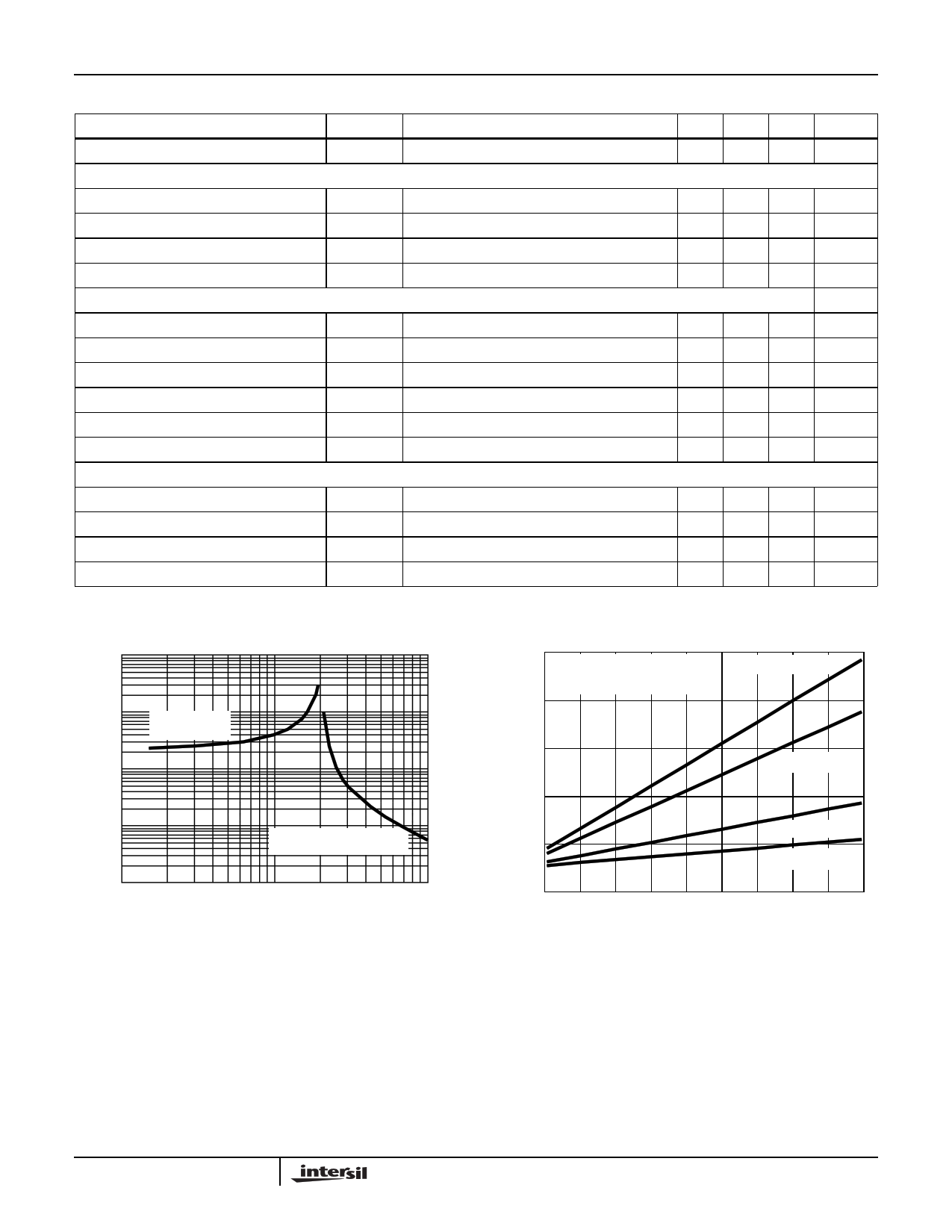

Typical Performance Curves

1000

100

RT PULLUP

TO +12V

10

RT PULLDOWN TO VSS

10 100 1000

SWITCHING FREQUENCY (kHz)

FIGURE 4. RT RESISTANCE vs FREQUENCY

100

CUGATE = CLGATE = CGATE

VVCC = 12V, VIN = 5V

80

CGATE = 4800pF

60

CGATE = 3600pF

40

CGATE = 1500pF

20

CGATE = 660pF

0

100 200 300 400 500 600 700 800 900 1000

SWITCHING FREQUENCY (kHz)

FIGURE 5. BIAS SUPPLY CURRENT vs FREQUENCY

2-315

5 Page

HIP6028

+5VIN

+3.3VIN

CIN

VOUT3

Q3

VOUT2

+12V

CVCC

COCSET

VCC GND

VIN2

OCSET

ROCSET

UGATE Q1

DRIVE3

PHASE

HIP6028

Q2

VOUT2 LGATE

LOUT1 VOUT1

COUT1

CR1

SS PGND

CSS

COUT2 KEY

ISLAND ON POWER PLANE LAYER

ISLAND ON CIRCUIT PLANE LAYER

VIA CONNECTION TO GROUND PLANE

FIGURE 11. PRINTED CIRCUIT BOARD POWER PLANES AND

ISLANDS

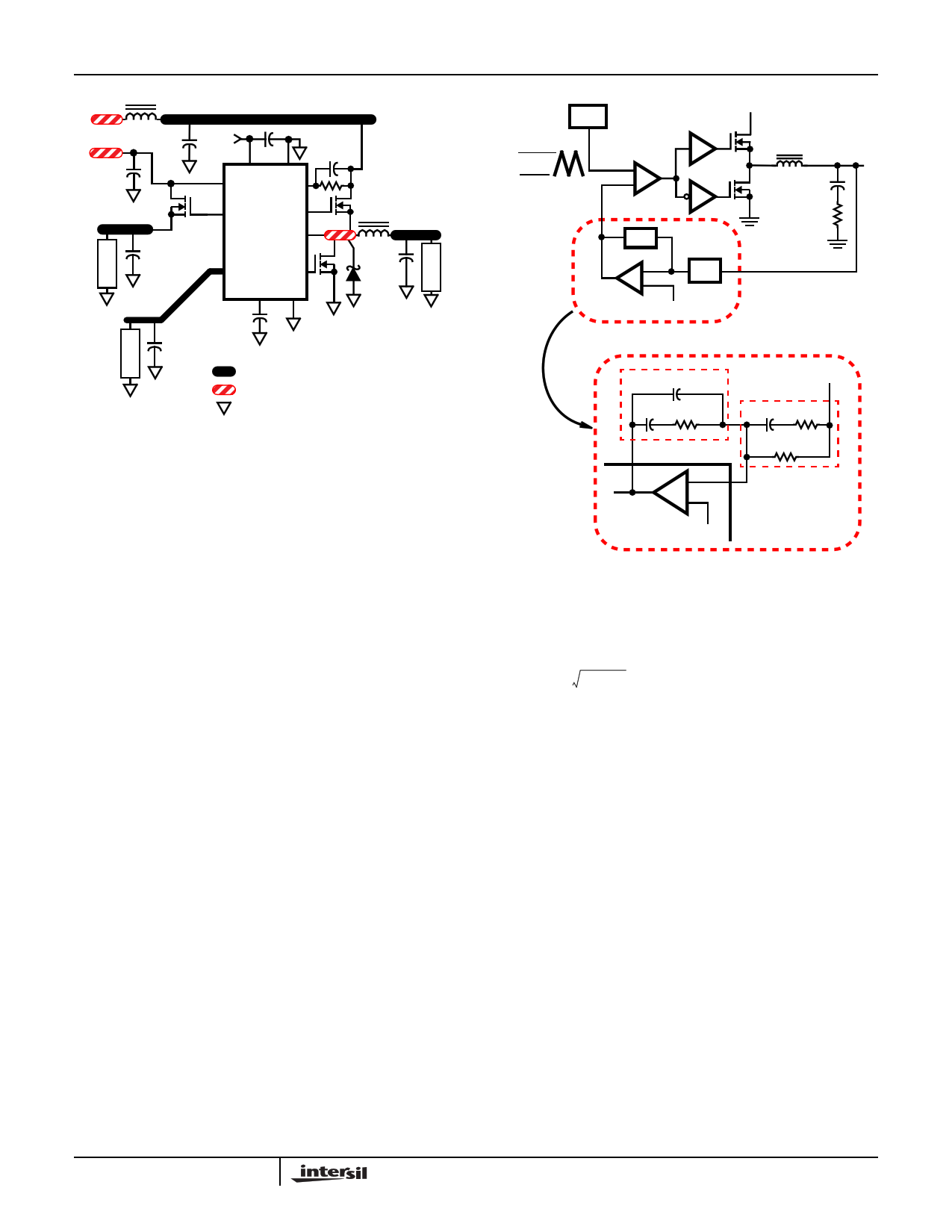

A multi-layer printed circuit board is recommended. Figure 11

shows the connections of the critical components in the

converter. Note that capacitors CIN and COUT could each

represent numerous physical capacitors. Dedicate one solid

layer for a ground plane and make all critical component

ground connections with vias to this layer. Dedicate another

solid layer as a power plane and break this plane into

smaller islands of common voltage levels. The power plane

should support the input power and output power nodes.

Use copper filled polygons on the top and bottom circuit

layers for the phase nodes. Use the remaining printed circuit

layers for small signal wiring. The wiring traces from the

control IC to the MOSFET gate and source should be sized

to carry 1A currents. The traces for VOUT2 need only be

sized for 0.2A. Locate COUT2 close to the HIP6028 IC.

PWM Controller Feedback Compensation

Both PWM controllers use voltage-mode control for output

regulation. This section highlights the design consideration

for a voltage-mode controller. Apply the methods and

considerations to both PWM controllers.

Figure 12 highlights the voltage-mode control loop for a

synchronous-rectified buck converter. The output voltage is

regulated to the reference voltage level. The reference

voltage level is the DAC output voltage for the PWM

controller. The error amplifier output (VE/A) is compared with

the oscillator (OSC) triangular wave to provide a pulse-width

modulated wave with an amplitude of VIN at the PHASE node.

The PWM wave is smoothed by the output filter (LO and CO).

The modulator transfer function is the small-signal transfer

function of VOUT/VE/A. This function is dominated by a DC

gain and the output filter, with a double pole break frequency

at FLC and a zero at FESR. The DC gain of the modulator is

simply the input voltage, VIN, divided by the peak-to-peak

oscillator voltage, ∆VOSC.

2-321

∆VOSC

OSC

PWM

COMP

-

+

DRIVER

DRIVER

ZFB

VE/A

- ZIN

+

ERROR

AMP

REFERENCE

VIN

LO VOUT

PHASE

CO

ESR

(PARASITIC)

DETAILED FEEDBACK COMPENSATION

C2

C1 R2

ZFB

VOUT

ZIN

C3 R3

COMP

- FB

+

HIP6028

REFERENCE

R1

FIGURE 12. VOLTAGE-MODE BUCK CONVERTER

COMPENSATION DESIGN

Modulator Break Frequency Equations

FLC=

-------------------1--------------------

2π × LO × CO

FESR= -2---π-----×-----E----S--1---R------×-----C----O---

The compensation network consists of the error amplifier

internal to the HIP6028 and the impedance networks ZIN

and ZFB. The goal of the compensation network is to provide

a closed loop transfer function with an acceptable 0dB

crossing frequency (f0dB) and adequate phase margin.

Phase margin is the difference between the closed loop

phase at f0dB and 180 degrees. The equations below relate

the compensation network’s poles, zeros and gain to the

components (R1, R2, R3, C1, C2, and C3) in Figure 12.

Use these guidelines for locating the poles and zeros of the

compensation network:

1. Pick Gain (R2/R1) for desired converter bandwidth

2. Place 1ST Zero Below Filter’s Double Pole (~75% FLC)

3. Place 2ND Zero at Filter’s Double Pole

4. Place 1ST Pole at the ESR Zero

5. Place 2ND Pole at Half the Switching Frequency

6. Check Gain against Error Amplifier’s Open-Loop Gain

7. Estimate Phase Margin - Repeat if Necessary

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet HIP6028EVAL1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HIP6028EVAL1 | Advanced PWM and Dual Linear Power Control with Integrated ACPI Support Interface | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |