|

|

PDF HIP6501EVAL1 Data sheet ( Hoja de datos )

| Número de pieza | HIP6501EVAL1 | |

| Descripción | Triple Linear Power Controller with ACPI Control Interface | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HIP6501EVAL1 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

Data Sheet

HIP6501A

February 2000 File Number 4749.2

Triple Linear Power Controller with ACPI

Control Interface

The HIP6501A, paired with either the HIP6020 or HIP6021,

simplifies the implementation of ACPI-compliant designs in

microprocessor and computer applications. The IC

integrates two linear controllers and a low-current pass

transistor, as well as the monitoring and control functions

into a 16-pin SOIC package. One linear controller generates

the 3.3VDUAL voltage plane from an ATX power supply’s

5VSB output during sleep states (S3, S4/S5), powering the

PCI slots through an external pass transistor, as instructed

by the status of the 3.3VDUAL enable pin. An additional pass

transistor is used to switch in the ATX 3.3V output for PCI

operation during S0 and S1 (active) operatingstates. The

second linear controller supplies the computer system’s

2.5V/3.3V memory power through an external pass

transistor in active states. During S3 state, an integrated

pass transistor supplies the 2.5V/3.3V sleep-state power. A

third controller powers up a 5VDUAL plane by switching in

the ATX 5V output in active states, or the ATX 5VSB in sleep

states.

The HIP6501A’s operating mode (active-state outputs or

sleep-state outputs) is selectable through two control pins:

S3 and S5. Further control of the logic governing activation

of different power modes is offered through two enabling

pins: EN3VDL and EN5VDL. In active states, the 3.3VDUAL

linear regulator uses an external N-Channel pass MOSFET

to connect the output (VOUT1) directly to the 3.3V input

supplied by an ATX (or equivalent) power supply, while

incurring minimal losses. In sleep state, the 3.3VDUAL output

is supplied from the ATX 5VSB through an NPN transistor,

also external to the controller. Active state power delivery for

the 2.5/3.3VMEM output is done through an external NPN

transistor, or an NMOS switch for the 3.3V setting. In sleep

states, conduction on this output is transferred to an internal

pass transistor. The 5VDUAL output is powered through two

external MOS transistors. In sleep states, a PMOS (or PNP)

transistor conducts the current from the ATX 5VSB output,

while in active states, current flow is transferred to an NMOS

transistor connected to the ATX 5V output. Similar to the

3.3VDUAL output, the operation of the 5VDUAL output is

dictated not only by the status of the S3 and S5 pins, but that

of the EN5VDL pin as well.

Ordering Information

PART NUMBER

HIP6501ACB

HIP6501EVAL1

TEMP.

RANGE (oC)

PACKAGE

0 to 70 16 Ld SOIC

Evaluation Board

PKG.

NO.

M16.15

Features

• Provides 3 ACPI-Controlled Voltages

- 5V Active/Sleep (5VDUAL)

- 3.3V Active/Sleep (3.3VDUAL)

- 2.5V/3.3V Active/Sleep (2.5VMEM)

• Simple Control Design - No Compensation Required

• Excellent Output Voltage Regulation

- 3.3VDUAL Output: ±2.0% Over Temperature; Sleep

States Only

- 2.5V/3.3V Output: ±2.0% Over Temperature; Both

Operational States (3.3V setting in sleep only)

• Fixed Output Voltages Require No Precision External

Resistors

• Small Size

- Small External Component Count

• Selectable 2.5VMEM Output Voltage Via FAULT/MSEL Pin

- 2.5V for RDRAM Memory

- 3.3V for SDRAM Memory

• Under-Voltage Monitoring of All Outputs with Centralized

FAULT Reporting

• Adjustable Soft-Start Function Eliminates 5VSB

Perturbations

Pinout

HIP6501A (SOIC)

TOP VIEW

5VSB 1

EN3VDL 2

3V3DLSB 3

3V3DL 4

EN5VDL 5

S3 6

S5 7

GND 8

16 VSEN2

15 DRV2

14 12V

13 SS

12 5VDL

11 5VDLSB

10 DLA

9 FAULT/MSEL

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 2000

1 page

HIP6501A

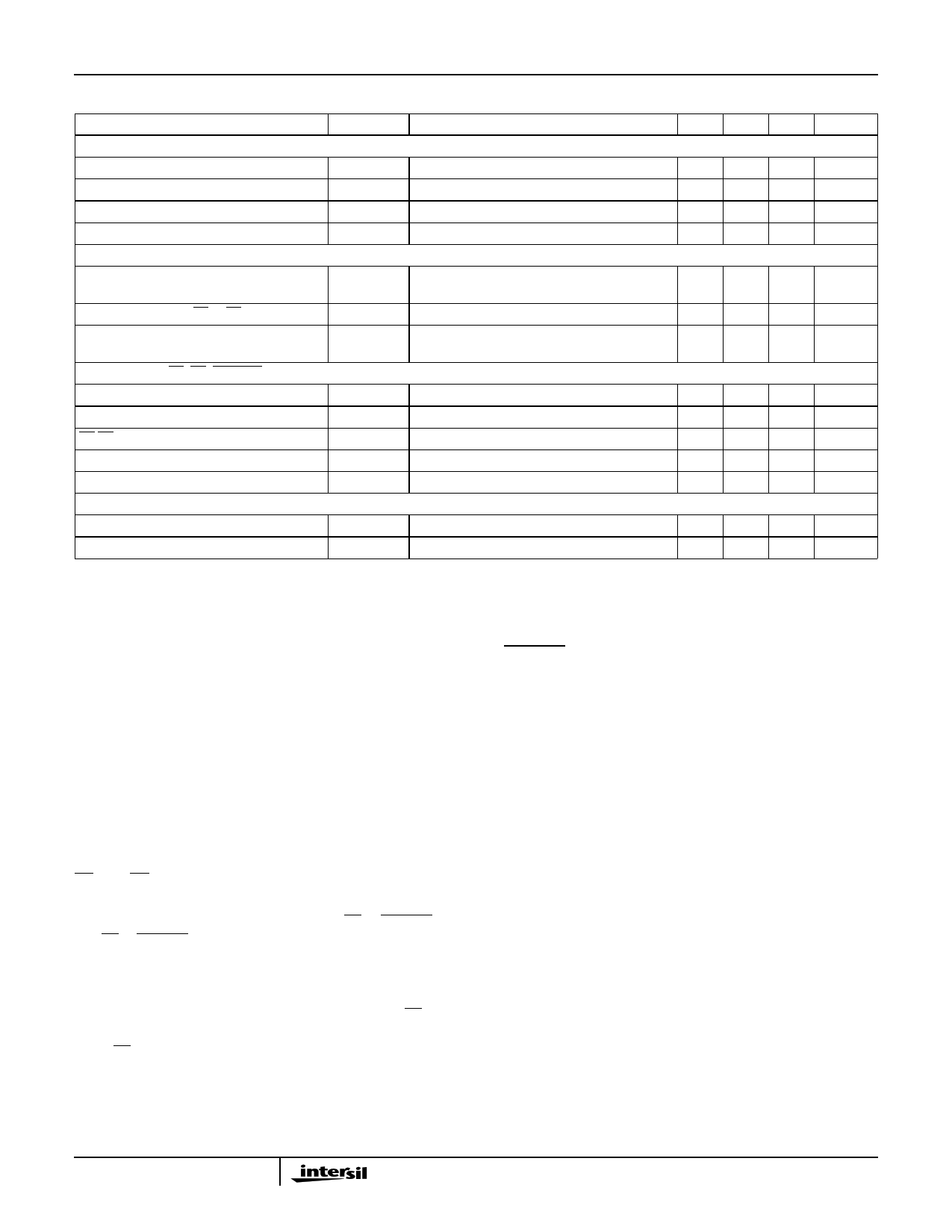

Electrical Specifications Recommended Operating Conditions, Unless Otherwise Noted. Refer to Figures 1, 2 and 3 (Continued)

PARAMETER

5VDUAL SWITCH CONTROLLER (VOUT3)

5VDL Under-Voltage Rising Threshold

SYMBOL

TEST CONDITIONS

MIN TYP MAX UNITS

- 3.750 -

V

5VDL Under-Voltage Hysteresis

- 260 -

mV

5VDLSB Output Drive Current

5VDLSB Pull-up Impedance to 5VSB

TIMING INTERVALS

Active State Assessment Past 12V

Threshold

Maximum Allowable S3 to S5 Skew

5VSB POR Extension Past Threshold

Voltage

I5VDLSB 5VDLSB = 4V

Note 2

-20 - -40

- 350 -

40 50 60

- 200 -

- 3.3 -

mA

Ω

ms

µs

ms

CONTROL I/O (S3, S5, EN3VDL, EN5VDL, FAULT)

High Level Threshold

Low Level Threshold

S3,S5 Internal Pull-up Impedance to 5VSB

FAULT Output Impedance

FAULT Under-Voltage Reporting Delay

TEMPERATURE MONITOR

Fault-Level Threshold

Shutdown-Level Threshold

FAULT = high

Note 3

Note 3

- - 2.2

0.8 -

-

- 70 -

- 100 -

- 10 -

125 -

- 150

-

-

V

V

kΩ

Ω

µs

oC

oC

NOTES:

2. Guaranteed by Correlation.

3. Guaranteed by Design.

Functional Pin Description

5VSB (Pin 1)

Provide a 5V bias supply for the IC to this pin by connecting

it to the ATX 5VSB output. This pin also provides the base

bias current for all the external NPN transistors controlled by

the IC. The voltage at this pin is monitored for power-on

reset (POR) purposes.

GND (Pin 8)

Signal ground for the IC. All voltage levels are measured with

respect to this pin.

S3 and S5 (Pins 6 and 7)

These pins switch the IC’s operating state from active (S0,

S1) to S3 and S4/S5 sleep states. Connect S3 to SLP_S3

and S5 to SLP_S5. These are digital inputs featuring internal

70kΩ (typical) resistor pull-ups to 5VSB. Internal circuitry de-

glitches the S3 pin for disturbances. Additional circuitry

blocks any illegal state transitions (such as S3 to S4/S5 or

vice versa). When entering an S4/S5 sleep state, the S3

signal is allowed to go low as far as 200µs (typically) ahead

of the S5 signal.

EN3VDL and EN5VDL (Pins 2 and 5)

These pins control the logic governing the output behavior in

response to S3 and S4/S5 requests. These are digital inputs

whose status can only be changed during active states

operation or during chip shutdown (SS pin grounded by

external open-drain device). The input information is latched-

in when entering a sleep state, as well as following 5VSB

POR release or exit from shutdown.

FAULT/MSEL (Pin 9)

This is a multiplexed function pin allowing the setting of the

memory output voltage to either 2.5V or 3.3V (for RDRAM or

SDRAM memory systems). The memory voltage setting is

latched-in 3ms (typically) after 5VSB POR release. In case

of an under-voltage on any of the outputs or an over-

temperature event, this pin is used to report the fault

condition by being pulled to 5VSB.

SS (Pin 13)

Connect a small ceramic capacitor (allowable range: 5nF-

0.22µF; 0.1µF recommended) from this pin to GND. The

internal Soft-Start (SS) current source along with the

external capacitor creates a voltage ramp used to control the

ramp-up of the output voltages. Pulling this pin low with an

open-drain device shuts down all the outputs as well as

5

5 Page

HIP6501A

capacitance (aluminum electrolytics or tantalum capacitors)

placement is not as critical as the high-frequency capacitor

placement, but having these capacitors close to the load

they serve is preferable.

The only critical small signal component is the soft-start

capacitor, CSS. Locate this component close to SS pin of the

control IC and connect to ground through a via placed close

to the capacitor’s ground pad. Minimize any leakage current

paths from SS node, since the internal current source is only

10µA.

A multi-layer printed circuit board is recommended. Figure

12 shows the connections of most of the components in the

converter. Note that the individual capacitors each could

represent numerous physical capacitors. Dedicate one solid

layer for a ground plane and make all critical component

ground connections through vias placed as close to the

component as possible. Dedicate another solid layer as a

power plane and break this plane into smaller islands of

common voltage levels. Ideally, the power plane should

support both the input power and output power nodes. Use

copper filled polygons on the top and bottom circuit layers to

create power islands connecting the filtering components

(output capacitors) and the loads. Use the remaining printed

circuit layers for small signal wiring.

Component Selection Guidelines

Output Capacitors Selection

The output capacitors for all outputs should be selected to

allow the output voltage to meet the dynamic regulation

requirements of active state operation (S0, S1). The load

transient for the various microprocessor system’s

components may require high quality capacitors to supply

the high slew rate (di/dt) current demands. Thus, it is

recommended that capacitors COUT1 and COUT2 should be

selected for transient load regulation.

Also, during the transition between active and sleep states,

there is a short interval of time during which none of the

power pass elements are conducting - during this time the

output capacitors have to supply all the output current. The

output voltage drop during this brief period of time can be

approximated with the following formula:

∆VO U T

=

IO

U

T

×

E

S

RO

U

T

+

C-----O---t--tU-----T--

, where

∆VOUT - output voltage drop

ESROUT - output capacitor bank ESR

IOUT - output current during transition

COUT - output capacitor bank capacitance

tt - active-to-sleep or sleep-to-active transition time (10µs

typical)

Since the output voltage drop is heavily dependent on the

ESR (equivalent series resistance) of the output capacitor

bank, the capacitors should be chosen to maintain the

output voltage above the lowest allowable regulation level.

Input Capacitors Selection

The input capacitors for an HIP6501A application must have

sufficiently low ESR so that the input voltage does not dip

excessively when energy is transferred to the output

capacitors. If the ATX supply does not meet the

specifications, certain imbalances between the ATX’s

outputs and the HIP6501A’s regulation levels could result in

a brisk transfer of energy from the input capacitors to the

supplied outputs. When transiting from active to sleep

states, this phenomena could result in the 5VSB voltage

dropping below the POR level (typically 4.3V) and

temporarily disabling the HIP6501A. The solution to this

potential problem is to use larger input capacitors (on 5VSB)

with a lower total combined ESR.

Transistor Selection/Considerations

The HIP6501A typically requires one P-Channel and two

N-Channel power MOSFETs and two bipolar NPN transistors.

One general requirement for selection of transistors for all

the linear regulators/switching elements is package selection

for efficient removal of heat. The power dissipated in a linear

regulator/switching element is:

PLINEAR = IO × (VIN – VOUT)

Select a package and heatsink that maintains the junction

temperature below the rating with the maximum expected

ambient temperature.

Q1

The active element on the 2.5V/3.3VMEM output has

different requirements for each of the two voltage settings. In

2.5V systems utilizing RDRAM (or voltage-compatible)

memory, Q1 must be a bipolar NPN capable of conducting

the maximum required output current and it must have a

minimum current gain (hfe) of 100-150 at this current and

0.7V VCE. In such systems, the 2.5V output is regulated

from the ATX 3.3V output while in an active state. In 3.3V

systems (SDRAM or compatible) Q1 must be an N-Channel

MOSFET, since the MOSFET serves as a switch during

active states (S0, S1). The main criteria for the selection of

this transistor is output voltage budgeting. The maximum

rDS(ON) allowed at highest junction temperature can be

expressed with the following equation:

rDS(ON) MAX = -V----I--N-------M-I--O--I--N-U-----T–-----V-M---O--A---U--X---T----M-----I--N-- , where

VIN MIN - minimum input voltage

VOUT MIN - minimum output voltage allowed

IOUT MAX - maximum output current

The gate bias available for this MOSFET is approximately 8V.

11

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet HIP6501EVAL1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HIP6501EVAL1 | Triple Linear Power Controller with ACPI Control Interface | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |