|

|

PDF AD7091 Data sheet ( Hoja de datos )

| Número de pieza | AD7091 | |

| Descripción | 12-Bit ADC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD7091 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

Data Sheet

FEATURES

Fast throughput rate of 1 MSPS

Specified for VDD of 2.09 V to 5.25 V

INL of ±1 LSB maximum

Analog input range of 0 V to VDD

Ultralow power

367 μA typical at 3 V and 1 MSPS

324 nA typical at 3 V in power-down mode

Reference provided by VDD

Flexible power/throughput rate management

High speed serial interface: SPI®-/QSPI™-/MICROWIRE®-/

DSP-compatible

Busy indicator

Power-down mode

8-lead, 2 mm × 2 mm LFCSP package

Temperature range: −40°C to +125°C

APPLICATIONS

Battery-powered systems

Handheld meters

Medical instruments

Mobile communications

Instrumentation and control systems

Data acquisition systems

Optical sensors

Diagnostic/monitoring functions

Energy harvesting

GENERAL DESCRIPTION

The AD7091 is a 12-bit successive approximation register

analog-to-digital converter (SAR ADC) that offers ultralow

power consumption (typically 367 μA at 3 V and 1 MSPS) while

achieving fast throughput rates (1 MSPS with a 50 MHz SCLK).

The AD7091 operates from a single 2.09 V to 5.25 V power

supply. The AD7091 also features an on-chip conversion clock

and a high speed serial interface.

The conversion process and data acquisition are controlled using

a CONVST signal and an internal oscillator. The AD7091 has a

serial interface that allows data to be read after the conversion

while achieving a 1 MSPS throughput rate. The AD7091 uses

advanced design and process techniques to achieve very low

power dissipation at high throughput rates.

1 MSPS, Ultralow Power,

12-Bit ADC in 8-Lead LFCSP

AD7091

FUNCTIONAL BLOCK DIAGRAM

REGCAP

VDD

AD7091

VIN T/H

12-BIT

SAR

ADC

SERIAL

INTERFACE

SDO

SCLK

CS

CONVERSION

CONTROL LOGIC

CLK

OSC

CONVST

GND

Figure 1.

1100

VDD = 3V

1000

900

800

700

600

500

400

300

200

100

0

0 200 400 600 800

THROUGHPUT RATE (kSPS)

Figure 2. Power Dissipation vs. Throughput Rate

1000

The reference is derived internally from VDD. This design allows

the widest dynamic input range to the ADC; that is, the analog

input range for the AD7091 is from 0 V to VDD.

PRODUCT HIGHLIGHTS

1. Lowest Power 12-Bit SAR ADC Available.

2. High Throughput Rate with Ultralow Power Consumption.

3. Flexible Power/Throughput Rate Management.

Average power scales with the throughput rate. Power-down

mode allows the average power consumption to be reduced

when the device is not performing a conversion.

4. Reference Derived from the Power Supply.

5. Single-Supply Operation.

Rev. A

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2012–2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

Free Datasheet http://www.nDatasheet.com

1 page

AD7091

Data Sheet

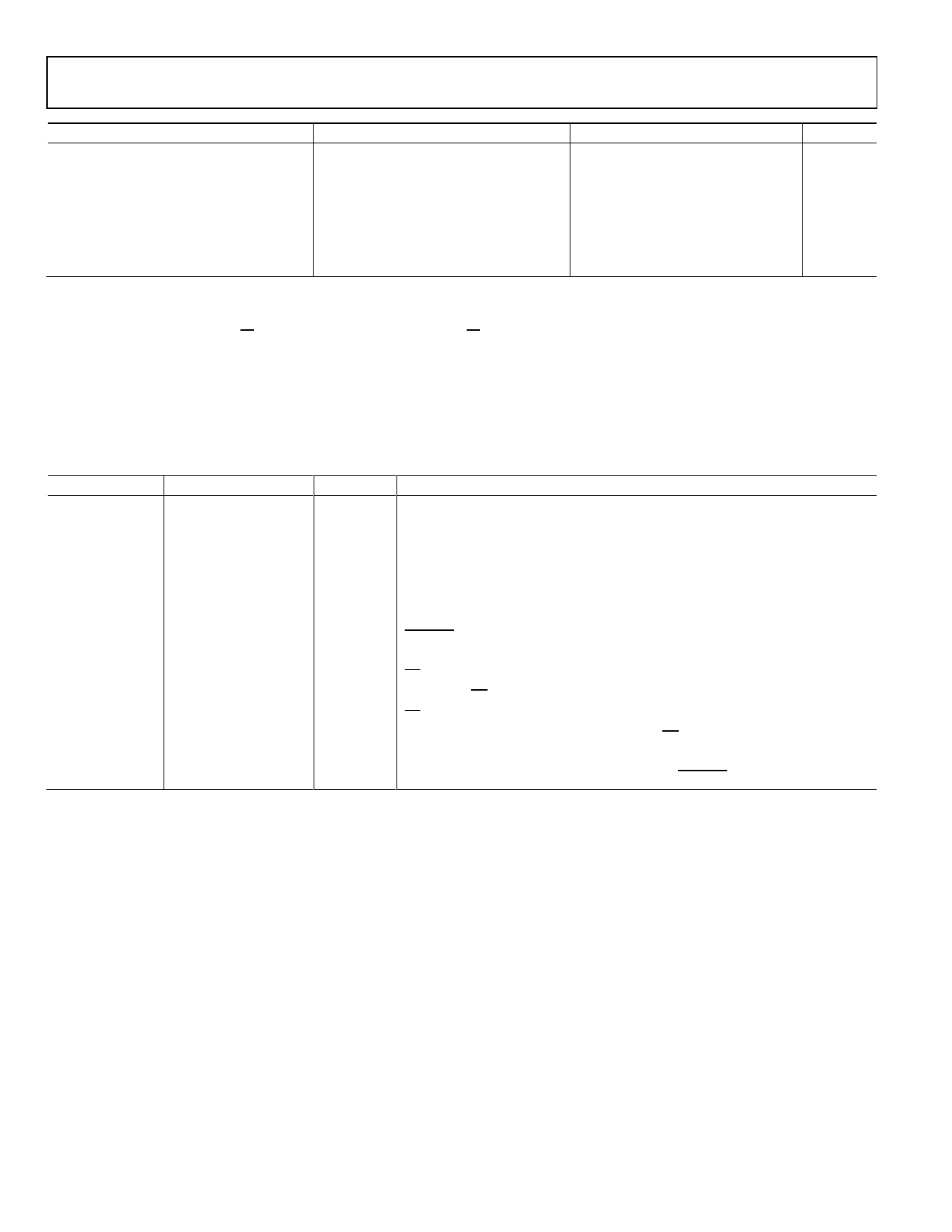

Parameter

Power Dissipation

Normal Mode—Static4

Normal Mode—Operational

Power-Down Mode

Test Conditions/Comments

VIN = 0 V

VDD = 5.25 V

VDD = 3 V

VDD = 5.25 V, fSAMPLE = 1 MSPS

VDD = 3 V, fSAMPLE = 1 MSPS

VDD = 5.25 V

VDD = 3 V

Min Typ Max Unit

50 142 µW

27 84

µW

2.4 3

mW

1.1 1.4

mW

2 44 µW

1 24 µW

1 Dynamic performance is achieved when SCLK operates in burst mode. Operating a free running SCLK during the acquisition phase degrades dynamic performance.

2 See the Terminology section.

3 Sample tested during initial release to ensure compliance.

4 SCLK is operating in burst mode and CS is idling high. With a free running SCLK and CS pulled low, the IDD static current is increased by 60 µA typical at VDD = 5.25 V.

TIMING SPECIFICATIONS

VDD = 2.09 V to 5.25 V, TA = −40°C to +125°C, unless otherwise noted. Signals are specified from 10% to 90% of VDD with a load

capacitance of 12 pF on the output pin.1

Table 2.

Parameter

fSCLK

t1

t2

t3

t4

t5

t6

t7

t8

t9

t10

t11

t12

t13

tQUIET

Limit at TMIN, TMAX

50

8

7

0.4 tSCLK

3

0.4 tSCLK

15

10

650

6

18

8

8

100

50

Unit

MHz max

ns max

ns max

ns min

ns min

ns min

ns max

ns min

ns max

ns min

ns max

ns min

ns min

µs max

ns min

Description

Frequency of serial read clock

Delay from the end of a conversion until SDO exits the three-state condition

Data access time after SCLK falling edge

SCLK high pulse width

SCLK to data valid hold time

SCLK low pulse width

SCLK falling edge to SDO high impedance

CONVST pulse width

Conversion time

CS low time before the end of a conversion

Delay from CS falling edge until SDO exits the three-state condition

CS high time before the end of a conversion

Delay from the end of a conversion until the CS falling edge

Power-up time

Time between the last SCLK edge and the next CONVST pulse

1 Sample tested during initial release to ensure compliance.

Rev. A | Page 4 of 20

Free Datasheet http://www.nDatasheet.com

5 Page

AD7091

THEORY OF OPERATION

CIRCUIT INFORMATION

The AD7091 is a 12-bit successive approximation register

analog-to-digital converter (SAR ADC) that offers ultralow

power consumption (typically 367 µA at 3 V and 1 MSPS) while

achieving fast throughput rates (1 MSPS with a 50 MHz SCLK).

The part operates from a single power supply in the range of

2.09 V to 5.25 V.

The AD7091 provides an on-chip track-and-hold amplifier

and an analog-to-digital converter (ADC) with a serial interface

housed in a tiny 8-lead LFCSP package. This package offers

considerable space-saving advantages compared with alternative

solutions. The serial clock input accesses data from the part. The

clock for the SAR ADC is generated internally.

The analog input range is 0 V to VDD. An external reference is

not required for the ADC, nor is there a reference on chip. The

reference voltage for the AD7091 is derived from the power

supply and, thus, provides the widest dynamic input range of

0 V to VDD.

The AD7091 also features a power-down option to save power

between conversions. The power-down feature is implemented

using the standard serial interface, as described in the Modes of

Operation section.

CONVERTER OPERATION

The AD7091 is a SAR ADC based around a charge redistribu-

tion DAC. Figure 15 and Figure 16 show simplified schematics

of the ADC.

Figure 15 shows the ADC during its acquisition phase; SW2 is

closed and SW1 is in Position A. The comparator is held in a

balanced condition, and the sampling capacitor acquires the

signal on VIN.

CHARGE

REDISTRIBUTION

DAC

SAMPLING

A CAPACITOR

VIN

SW1

B ACQUISITION

PHASE

SW2

CONTROL

LOGIC

GND

COMPARATOR

LDO/2

Figure 15. ADC Acquisition Phase

Data Sheet

When the ADC starts a conversion, SW2 opens and SW1 moves

to Position B, causing the comparator to become unbalanced (see

Figure 16). The control logic and the charge redistribution DAC

are used to add and subtract fixed amounts of charge from the

sampling capacitor to bring the comparator back into a balanced

condition. When the comparator is rebalanced, the conversion

is complete. The control logic generates the ADC output code.

Figure 17 shows the ADC transfer function.

CHARGE

REDISTRIBUTION

DAC

SAMPLING

A CAPACITOR

VIN

SW1

B CONVERSION SW2

PHASE

CONTROL

LOGIC

GND

COMPARATOR

LDO/2

Figure 16. ADC Conversion Phase

ADC TRANSFER FUNCTION

The output coding of the AD7091 is straight binary. The designed

code transitions occur midway between successive integer LSB

values, such as 0.5 LSB, 1.5 LSB, and so on. The LSB size for the

AD7091 is VDD/4096. The ideal transfer characteristic for the

AD7091 is shown in Figure 17.

111 ... 111

111 ... 110

111 ... 000

011 ... 111

1LSB = VDD /4096

000 ... 010

000 ... 001

000 ... 000

0V 1LSB

VDD

ANALOG INPUT

– 1LSB

Figure 17. AD7091 Transfer Characteristic

Rev. A | Page 10 of 20

Free Datasheet http://www.nDatasheet.com

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet AD7091.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD7091 | 12-Bit ADC | Analog Devices |

| AD7091R | 12-Bit ADC | Analog Devices |

| AD7091R-2 | 12-Bit SAR ADC | Analog Devices |

| AD7091R-4 | 12-Bit SAR ADC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |