|

|

PDF ICSLV810 Data sheet ( Hoja de datos )

| Número de pieza | ICSLV810 | |

| Descripción | BUFFER - CLOCK DRIVER | |

| Fabricantes | Integrated Device Technolog | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICSLV810 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

BUFFER/CLOCK DRIVER

DATASHEET

ICSLV810

Description

The ICSLV810 is a low skew 1.5 V to 2.5 V, 1:10 fanout

buffer. This device is specifically designed for data

communications clock management. The large fanout from

a single input line reduces loading on the input clock. The

TTL level outputs reduce noise levels on the part. Typical

applications are clock and signal distribution.

Features

• Packaged in 20-pin QSOP/SSOP

• Split 1:10 fanout Buffer

• Maximum skew between outputs of different packages

0.75 ns

• Max propagation delay of 3.8 ns

• Operating voltage of 1.5 V to 2.5 V on Bank A

• Operating voltage of 1.5 V to 2.5 V on Banks B and C

• Advanced, low power, CMOS process

• Industrial temperature range -40° C to +85° C

• 3.3 V tolerant input when VDDA=2.5 V

• Pb (lead) free packaging

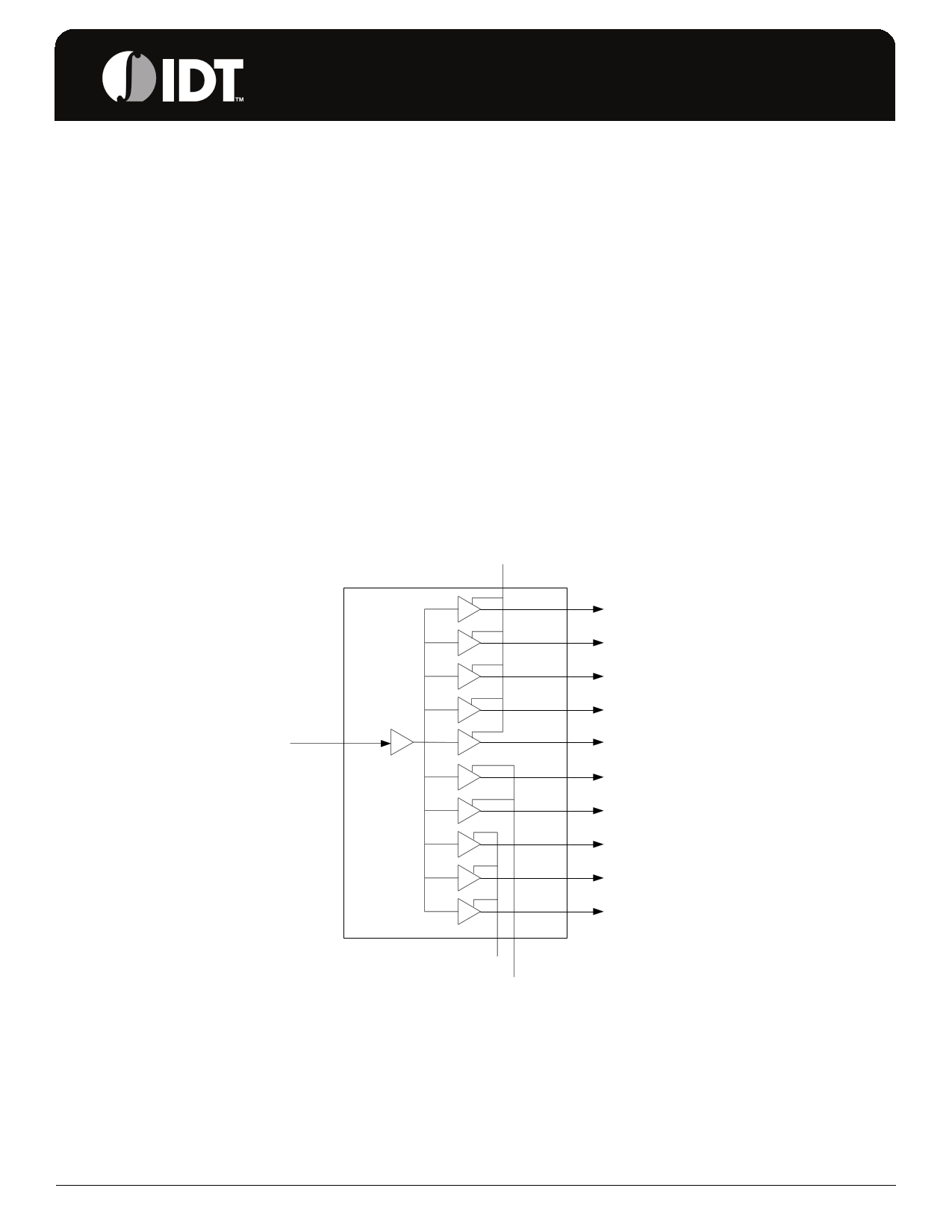

Block Diagram

VDDA

CLKIN

VDDB

VDDC

CLK 1

CLK 2

CLK 3

CLK 4

CLK 5

CLK 6

CLK 7

CLK 8

CLK 9

CLK 10

IDT™ / ICS™ BUFFER/CLOCK DRIVER

1

ICSLV810

REV H 051310

http://www.Datasheet4U.com

1 page

ICSLV810

BUFFER/CLOCK DRIVER

FAN OUT BUFFER

Parameter Symbol

Conditions

Output High Voltage VOH VDDB = 1.5 V

IOH = -7 mA

VIN = VIH or VIL

Output Low Voltage

VDDB = 2.5 V

IOH = -7 mA

VIN = VIH or VIL

VOL VDDB = 1.5 V

IOL =12 mA

VIN = VIH or VIL

VDDB = 2.5 V

IOL =12 mA

VIN = VIH or VIL

Input High Current

IIH VDDB = max

Input Low Current

IIL VDDB = max

Input High Current

II VDDB = max,

VIN = VDD (max)

Input Capacitance

CIN VIN = 0V, Note1

Output Capacitance COUT VOUT = 0V,

Note 1

Min.

1.1

1.8

Typ.

5

5.5

Note1: This parameter is not tested, guaranteed by design.

DC Electrical Characteristics—Bank C

VDDC = 2.5 V, Ambient Temperature -40° C to +85° C, unless otherwise noted

Parameter Symbol

Conditions

Min. Typ.

Operating Voltage VDDC

1.425

Quiescent Power

Supply Current

IDDC

VDDC = 2.5 V

No Load

F = 40 MHz

3m

VDDC = 1.5 V

No Load

F = 40 MHz

2m

Short Circuit Current IOS VDDC = 1.5 V

CLK6-7

±35

VDDC = 2.5 V

CLK6-7

±80

Output High Voltage

VOH VDDC = 1.5 V

IOH = -7 mA

VIN = VIH or VIL

1.1

Output Low Voltage

VDDC = 2.5 V

IOH = -7 mA

VIN = VIH or VIL

VOL VDDC = 1.5 V

IOL =12 mA

VIN = VIH or VIL

VDDC = 2.5 V

IOL =12 mA

VIN = VIH or VIL

1.8

Input High Current

IIH VDDC = max

Input Low Current

IIL VDDC = max

Max. Units

V

V

0.42 V

0.4 V

1 µA

-1 µA

20 µA

6.0 pF

8.0 pF

Max. Units

2.625

V

A

A

mA

mA

V

V

0.42 V

0.4 V

1 µA

-1 µA

IDT™ / ICS™ BUFFER/CLOCK DRIVER

5

ICSLV810

REV H 051310

5 Page

ICSLV810

BUFFER/CLOCK DRIVER

FAN OUT BUFFER

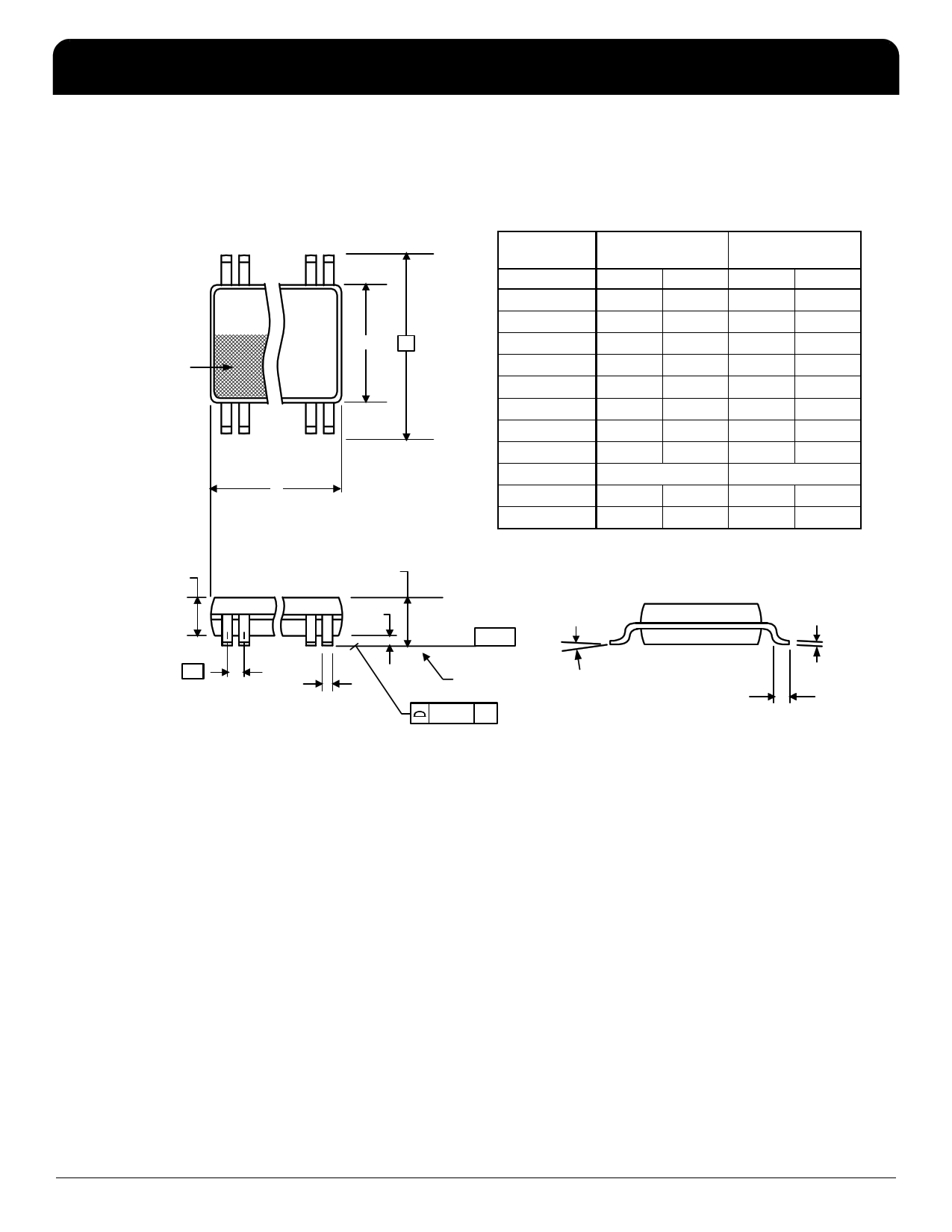

Package Outline and Package Dimensions (20-pin QSOP, 150 Mil. Body)

Package dimensions are kept current with JEDEC Publication No. 95

20

INDEX

AREA

12

D

A

2

e

b

Millimeters

Inches*

E1 E

A

Symbol

A

A1

A2

b

C

D

E

E1

e

L

α

Min Max

1.351 .75

0.10 0.25

-- 1.50

0.20 0.30

0.180 .25

8.558 .75

5.806 .20

3.80 4.00

0.635 Basic

0.401 .27

0° 8°

Min Max

.053. 069

.0040 .010

-- .059

0.008 0.012

.007. 010

.337. 344

.228. 244

.150 .157

0.025 Basic

.016. 050

0° 8°

*For reference only. Controlling dimensions in mm.

A

1

-C-

SEATING

PLANE

C.10 (.004)

c

L

IDT™ / ICS™ BUFFER/CLOCK DRIVER

11

ICSLV810

REV H 051310

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet ICSLV810.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICSLV810 | Buffer/Clock Driver | Integrated Circuit Systems |

| ICSLV810 | BUFFER - CLOCK DRIVER | Integrated Device Technolog |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |