|

|

PDF NB3L208K Data sheet ( Hoja de datos )

| Número de pieza | NB3L208K | |

| Descripción | 2.5V / 3.3V Differential 1:8 HCSL Fanout Buffer | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB3L208K (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

NB3L208K

2.5V, 3.3V Differential 1:8

HCSL Fanout Buffer

Description

The NB3L208K is a differential 1:8 Clock fanout buffer with

High−speed Current Steering Logic (HCSL) outputs. Inputs can

directly accept differential LVPECL, LVDS, and HCSL signals.

Single−ended LVPECL, HCSL, LVCMOS, or LVTTL levels are

accepted with a proper external Vth reference supply per Figures 4

and 6. The input signal will be translated to HCSL and provides eight

identical copies operating up to 350 MHz.

The NB3L208K is optimized for ultra−low phase noise, propagation

delay variation and low output–to–output skew, and is DB800H

compliant. As such, system designers can take advantage of the

NB3L208K’s performance to distribute low skew clocks across the

backplane or the motherboard making it ideal for Clock and Data

distribution applications such as PCI Express, FBDIMM, Networking,

Mobile Computing, Gigabit Ethernet, etc.

Output drive current is set by connecting a 475 W resistor from

IREF (Pin 27) to GND per Figure 11. Outputs can also interface to

LVDS receivers when terminated per Figure 12.

Features

• Maximum Input Clock Frequency > 350 MHz

• 2.5 V ±5% / 3.3 V ±10% Supply Voltage Operation

• 8 HCSL Outputs

• DB800H Compliant

• Individual OE Control Pin for Each Bank of 2 Outputs

• 100 ps Max Output−to−Output Skew Performance

• 1 ns Typical Propagation Delay

• 500 ps Typical Rise and Fall Times

• 80 fs Maximum Additive Phase Jitter RMS

• −40°C to +85°C Ambient Operating Temperature

• QFN 32−pin Package, 5 mm x 5 mm

• These Devices are Pb−Free and are RoHS Compliant

Typical Applications

• PCI Express

• FBDIMM

• Mobile Computing

• Networking

• Gigabit Ethernet

www.onsemi.com

MARKING

DIAGRAM

1 32

QFN32

G SUFFIX

CASE 488AM

1

NB3L

208K

AWLYYWWG

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb−Free Package

ORDERING INFORMATION

See detailed ordering and shipping information page 12 of this

data sheet.

© Semiconductor Components Industries, LLC, 2014

December, 2014 − Rev. 1

1

Publication Order Number:

NB3L208K/D

1 page

NB3L208K

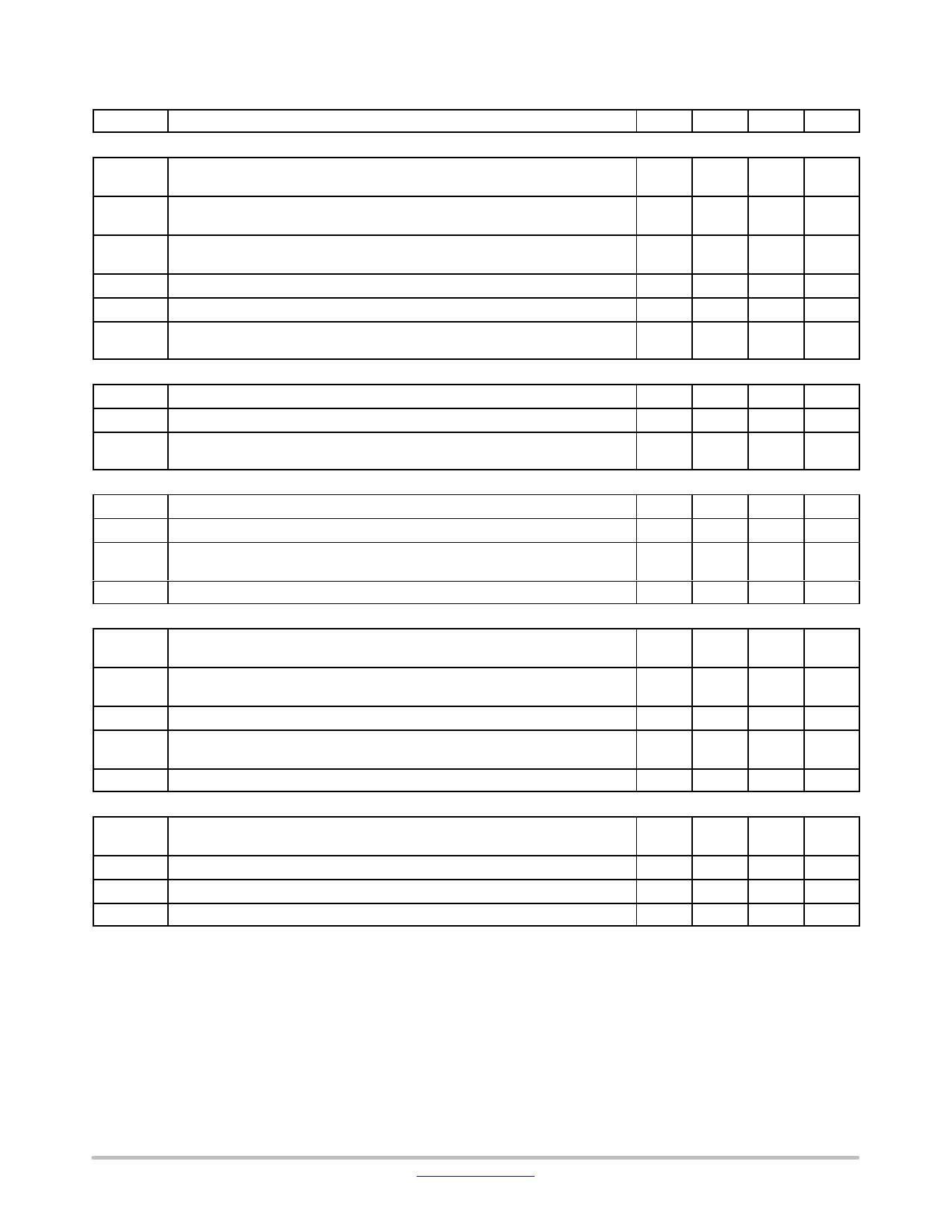

Table 4. DC CHARACTERISTICS VDD = VDD_O = 3.3 V ±10% or 2.5 V ±5%, TA = −40°C to 85°C

Symbol

Characteristics

Min Typ Max Unit

POWER SUPPLY CURRENT

VDD Core Power Supply Voltage

VDD = 3.3 V ±10%

VDD = 2.5 V ±5%

VDD_O Output Power Supply Voltage

VDD_O = 3.3 V ±10%

VDD_O = 2.5 V ±5%

IDD + IDD_O Total Power Supply Current (all outputs active @ 350 MHz, RREF = 412 W,

RL = 43 W)

Istdby Standby Current, all OE pins de−asserted with inputs @ 350 MHz

lincr Incremental output current for additional pair of outputs; One OE Enabled

Istdby + lincr Standby Current plus incremental current for one additional pair of differential

outputs; One OE Enabled @ 350 MHz

2.970 3.3 3.630

2.375 2.5 2.625

V

2.970 3.3 3.630

2.375 2.5 2.625

V

170 210 mA

50 65 mA

30 45 mA

80 110 mA

HCSL OUTPUTS (Notes 4, 5)

VOH

VOL

VOUT

Output HIGH Voltage

Output LOW Voltage

Output Swing (Single−Ended)

Output Swing (Differential)

660

−150

400

800

750

1500

850

mV

mV

mV

DIFFERENTIAL INPUT DRIVEN SINGLE−ENDED (Note 6) (Figures 4 and 6)

VIH CLK_IN/CLK_IN# Single-ended Input HIGH Voltage

VIL CLK_IN/CLK_IN# Single-ended Input LOW Voltage

Vth Input Threshold Reference Voltage Range (Note 7)

0.5

GND

0.25

VDD

VIH − 0.3

VDD −

1.0

V

V

V

VISE Single-ended Input Voltage (VIH − VIL)

DIFFERENTIAL INPUTS DRIVEN DIFFERENTIALLY (Note 8) (Figures 5 and 7)

0.5

VDD

V

VIHD Differential Input HIGH Voltage

0.5

VDD −

V

0.85

VILD Differential Input LOW Voltage

0

VIHD −

V

0.25

VID

VIHCMR

Differential Input Voltage (VIHD − VILD)

Input Common Mode Range (Differential Configuration) (Note 9) (Figure 8)

0.25

0.5

1.3

VDD −

0.85

V

V

IIL Input Leakage Current 0 < VIN < VDD (Note 10)

LVTTL / LVCMOS INPUTS (OE#_x)

−5 5 mA

VIH Input HIGH Voltage

2.0

VDD +

V

0.3

VIL Input LOW Voltage

−0.3 0.8 V

IIL Input LOW Current (VIN = GND)

−10 +10 mA

IIH Input HIGH Current (VIN = VDD)

100 mA

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm.

4. Test configuration is Rs = 33.2 W, RL = 49.9, CL = 2 pF, RREF = 475 W.

5. Measurement taken from Single−Ended waveform unless specified otherwise.

6. VIH, VIL, Vth and VISE parameters must be complied with simultaneously.

7. Vth is applied to the complementary input when operating in single−ended mode.

8. VIHD, VILD, VID and VCMR parameters must be complied with simultaneously.

9. The common mode voltage is defined as VIH.

10. Does not include inputs with pulldown resistors.

www.onsemi.com

5

5 Page

Skew measurement point

0.000 V

NB3L208K

High Duty Cycle%

TPeriod

Low Duty Cycle%

Figure 15. Differential (CLOCK – CLOCK#) Measurement Points (Tperiod, Duty Cycle)

Vcross(rel) Max

550

500

450

Crossing Point (mV)

400

350

For Vhigh < 700mV

Use Equ. 1

For Vhigh > 700mV

Use Equ. 2

300 Vcross(rel) Min

250

200

625 650 675 700 725 750 775 800 825 850

Vhigh Average (mV)

Equ 1: Vcross(rel) Max = 0.550 − 0.5(0.7 − Vhigh avg)

Equ 2: Vcross(rel) Min = 0.250 + 0.5(Vhigh avg − 0.7)

Figure 16. Vcross Range Clarification (Note 35)

35. The picture above illustrates the effect of Vhigh above and below 700 mV on the Vcross range. The purpose of this is to prevent a 250 mV

Vcross with an 850 mV Vhigh. In addition, this prevents the case of a 550 mV Vcross with a 660 mV Vhigh. The actual specification for Vcross

is dependent upon the measured amplitude of Vhigh.

www.onsemi.com

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet NB3L208K.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB3L208K | 2.5V / 3.3V Differential 1:8 HCSL Fanout Buffer | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |