|

|

PDF NB3N51054 Data sheet ( Hoja de datos )

| Número de pieza | NB3N51054 | |

| Descripción | Quad HCSL / LVDS Clock Generator | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB3N51054 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

NB3N51054

3.3 V, Crystal to 100 MHz

Quad HCSL/LVDS PCIe

Clock Generator

The NB3N51054 is a precision, low phase noise clock generator that

supports PCI Express requirements. The device accepts a 25 MHz

fundamental mode parallel resonant crystal or a 25 MHz reference

clock signal and generates four differential HCSL/LVDS outputs (See

Figure 7 for LVDS interface) at 100 MHz clock frequency with

maximum skew of 40 ps. Through I2C interface, NB3N51054

provides selectable spread spectrum options of −0.35% and −0.5% for

applications demanding low Electromagnetic Interface (EMI) as well

as optimum performance with no spread option. The I2C interface

further enables control of each output and they can be enabled/

disabled individually.

www.onsemi.com

MARKING

DIAGRAM

TSSOP−24

CASE 948H

NB3N5

1054G

ALYW

Features

• Uses 25 MHz Fundamental Crystal or Reference Clock Input

• Four Low Skew HCSL or LVDS Outputs

• I2C Support with Read Back Capability

• Spread of −0.35%, −0.5% and No Spread

• Individual Output Enable/Disable Control through I2C

• PCIe Gen 1, Gen 2, Gen 3 Compliant

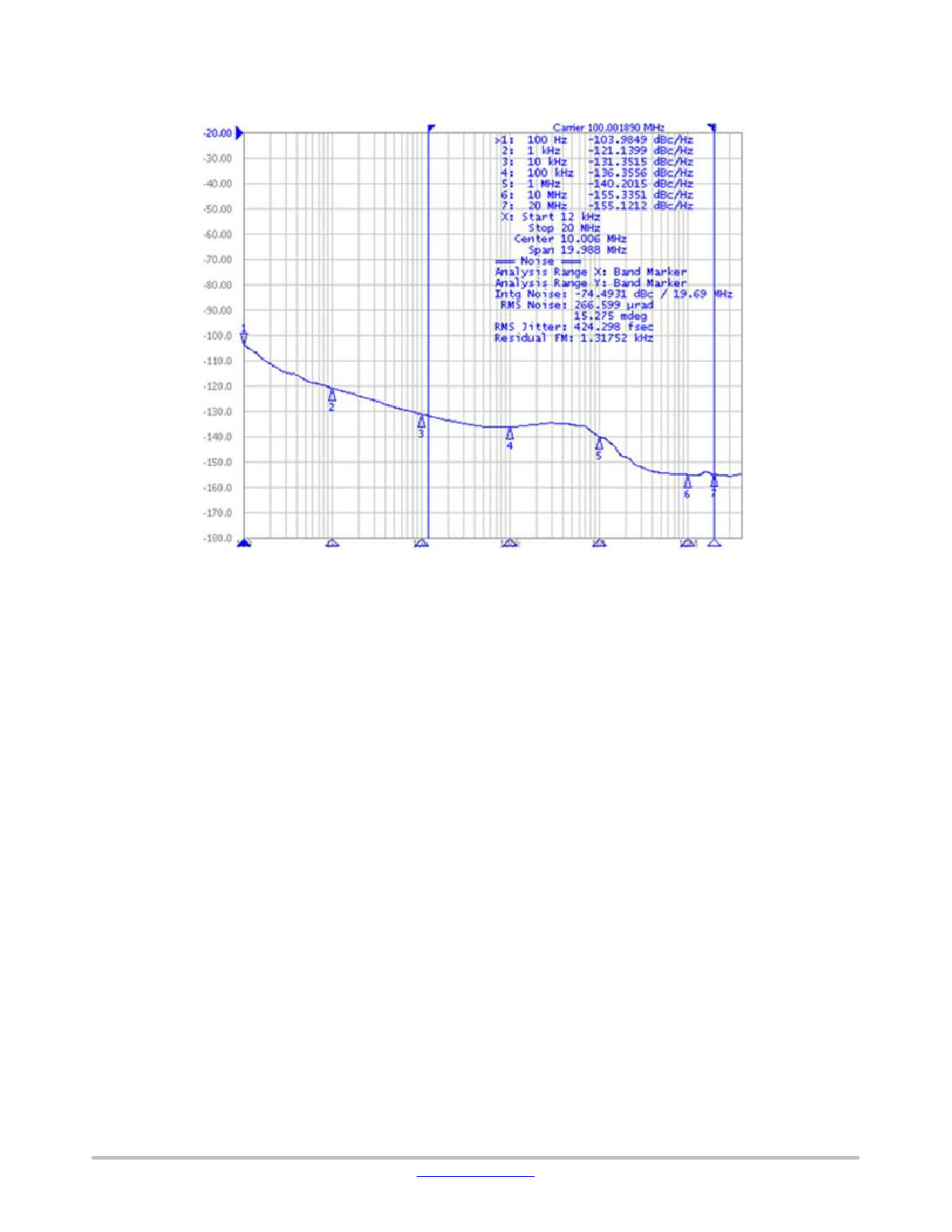

• Typical Phase Jitter @ 100 MHz (Integrated 12 kHz to 20 MHz):

0.5 ps

• Typical Cycle−Cycle Jitter @ 100 MHz (10k cycles): 20 ps

• Phase Noise @ 100 MHz:

Offset Noise Power

100 Hz −104 dBc/Hz

1 kHz −121 dBc/Hz

10 kHz −131 dBc/Hz

100 kHz −136 dBc/Hz

1 MHz −140 dBc/Hz

10 MHz −155 dBc/Hz

• Operating Power Supply: 3.3 V ± 5%

• Industrial Temperature Range: −40°C to 85°C

• Functionally Compatible with ICS841S104I with enhanced

performance

• These are Pb−Free Devices

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 14 of this data sheet.

Application

• Networking

• Consumer

• Computing and Peripherals

• Industrial Equipment

• PCIe Clock Generation Gen 1, Gen 2 and Gen 3

End Products

• Switch and Router

• Set Top Box, LCD TV

• Servers, Desktop Computers

• Automated Test Equipment

© Semiconductor Components Industries, LLC, 2015

May, 2015 − Rev. 2

1

Publication Order Number:

NB3N51054/D

1 page

NB3N51054

Table 4. BYTE READ AND BYTE WRITE PROTOCOL

Byte Write Protocol

Bit Description

1 Start

2:8 Slave addresses – 7 bits

9 Write = 0

10 Acknowledge from slave

11:18

Command code – 8 bit

‘10000000’ stands for byte operation,

bits[1:0] command code represents the offset

of the byte to be accessed

19 Acknowledge from slave

20:27

Data byte from master − 8 bits

28 Acknowledge from slave

29 Stop

Bit

1

2:8

9

10

11:18

19

20

21:27

28

29

30:37

38

39

Byte Read Protocol

Description

Start

Slave addresses – 7 bits

Write = 0

Acknowledge from slave

Command code – 8 bit

‘10000000’ stands for byte operation

bits[1:0] command code represents the offset of the byte

to be accessed

Acknowledge from slave

Repeat start

Slave address – 7 bits

Read = 1

Acknowledge from slave

Data byte from slave – 8 bits

Not Acknowledge from master stop

CONTROL REGISTERS

Table 5. BYTE 0: CONTROL REGISTER 0

Bit @Pup

Name

70

Reserved

61

CLK3_OE

51

CLK2_OE

41

CLK1_OE

31

CLK0_OE

21

10

00

Reserved

Reserved

Reserved

Description

Reserved

CLK3 Output Enable

0 = Disable (Hi−Z)

1 = Enable

CLK2 Output Enable

0 = Disable (Hi−Z)

1 = Enable

CLK1 Output Enable

0 = Disable (Hi−Z)

1 = Enable

CLK0 Output Enable

0 = Disable (Hi−Z)

1 = Enable

Reserved

Reserved

Reserved

www.onsemi.com

5

5 Page

NB3N51054

PHASE NOISE

OFFSET FREQUENCY (Hz)

Figure 3. Typical Phase Noise Plot at 100 MHz (fCLKIN = 25 MHz Crystal , fCLKOUT = 100 MHz,

RMS Phase Jitter = 424 fs for Integration Range of 12 kHz to 20 MHz, Output Termination = HCSL type)

www.onsemi.com

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet NB3N51054.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB3N51054 | Quad HCSL / LVDS Clock Generator | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |