|

|

PDF ATmega644RFR2 Data sheet ( Hoja de datos )

| Número de pieza | ATmega644RFR2 | |

| Descripción | 8-bit Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ATmega644RFR2 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ATmega2564/1284/644RFR2

Features

• Network support by hardware assisted Multiple PAN Address Filtering

• Advanced Hardware assisted Reduced Power Consumption

• High Performance, Low Power AVR® 8-Bit Microcontroller

• Advanced RISC Architecture

- 135 Powerful Instructions – Most Single Clock Cycle Execution

- 32x8 General Purpose Working Registers / On-Chip 2-cycle Multiplier

- Up to 16 MIPS Throughput at 16 MHz and 1.8V – Fully Static Operation

• Non-volatile Program and Data Memories

- 256K/128K/64K Bytes of In-System Self-Programmable Flash

• Endurance: 10’000 Write/Erase Cycles @ 125°C (25’000 Cycles @ 85°C)

- 8K/4K/2K Bytes EEPROM

• Endurance: 20’000 Write/Erase Cycles @ 125°C (100’000 Cycles @ 25°C)

- 32K/16K/8K Bytes Internal SRAM

• JTAG (IEEE std. 1149.1 compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash EEPROM, Fuses and Lock Bits through the JTAG interface

• Peripheral Features

- Multiple Timer/Counter & PWM channels

- Real Time Counter with Separate Oscillator

- 10-bit, 330 ks/s A/D Converter; Analog Comparator; On-chip Temperature Sensor

- Master/Slave SPI Serial Interface

- Two Programmable Serial USART

- Byte Oriented 2-wire Serial Interface

• Advanced Interrupt Handler and Power Save Modes

• Watchdog Timer with Separate On-Chip Oscillator

• Power-on Reset and Low Current Brown-Out Detector

• Fully integrated Low Power Transceiver for 2.4 GHz ISM Band

- High Power Amplifier support by TX spectrum side lobe suppression

- Supported Data Rates: 250 kb/s and 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm RX Sensitivity; TX Output Power up to 3.5 dBm

- Hardware Assisted MAC (Auto-Acknowledge, Auto-Retry)

- 32 Bit IEEE 802.15.4 Symbol Counter

- SFD-Detection, Spreading; De-Spreading; Framing ; CRC-16 Computation

- Antenna Diversity and TX/RX control / TX/RX 128 Byte Frame Buffer

• PLL synthesizer with 5 MHz and 500 kHz channel spacing for 2.4 GHz ISM Band

• Hardware Security (AES, True Random Generator)

• Integrated Crystal Oscillators (32.768 kHz & 16 MHz, external crystal needed)

• I/O and Package

- 33 Programmable I/O Lines

- 48-pad QFN (RoHS/Fully Green)

• Temperature Range: -40°C to 125°C Industrial

• Ultra Low Power consumption (1.8 to 3.6V) for AVR & Rx/Tx: 10.1mA/18.6 mA

- CPU Active Mode (16MHz): 4.1 mA

- 2.4GHz Transceiver: RX_ON 6.0 mA / TX 14.5 mA (maximum TX output power)

- Deep Sleep Mode: <700nA @ 25°C

• Speed Grade: 0 – 16 MHz @ 1.8 – 3.6V range with integrated voltage regulators

8-bit

Microcontroller

with Low Power

2.4GHz

Transceiver for

ZigBee and

IEEE 802.15.4

ATmega2564RFR2

ATmega1284RFR2

ATmega644RFR2

Applications

• ZigBee® / IEEE 802.15.4-2011/2006/2003™ – Full and Reduced Function Device

• General Purpose 2.4GHz ISM Band Transceiver with Microcontroller

• RF4CE, SP100, WirelessHART™, ISM Applications and IPv6 / 6LoWPAN

42073B-MCU Wireless-09/14

42073B-MCU Wireless-09/14

1

1 page

ATmega2564/1284/644RFR2

The device is manufactured using Atmel’s high-density nonvolatile memory technology.

The On-chip ISP Flash allows the program memory to be reprogrammed in-system

trough an SPI serial interface, by a conventional nonvolatile memory programmer, or by

on on-chip boot program running on the AVR core. The boot program can use any

interface to download the application program in the application Flash memory.

Software in the boot Flash section will continue to run while the application Flash

section is updated, providing true Read-While-Write operation. By combining an 8 bit

RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel

ATmega2564/1284/644RFR2 is a powerful microcontroller that provides a highly

flexible and cost effective solution to many embedded control applications.

The ATmega2564/1284/644RFR2 AVR is supported with a full suite of program and

system development tools including: C compiler, macro assemblers, program

debugger/simulators, in-circuit emulators, and evaluation kits.

3.2 Pin Descriptions

3.2.1 EVDD

3.2.2 DEVDD

3.2.3 AVDD

3.2.4 DVDD

3.2.5 DVSS

3.2.6 AVSS

3.2.7 Port B (PB7...PB0)

3.2.8 Port D (PD7...PD0)

3.2.9 Port E (PE7,PE5...PE0)

External analog supply voltage.

External digital supply voltage.

Regulated analog supply voltage (internally generated).

Regulated digital supply voltage (internally generated).

Digital ground.

Analog ground.

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port B output buffers have symmetrical drive characteristics with both high sink

and source capability. As inputs, Port B pins that are externally pulled low will source

current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port B also provides functions of various special features of the

ATmega2564/1284/644RFR2.

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port D output buffers have symmetrical drive characteristics with both high sink

and source capability. As inputs, Port D pins that are externally pulled low will source

current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port D also provides functions of various special features of the

ATmega2564/1284/644RFR2.

Internally Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected

for each bit). The Port E output buffers have symmetrical drive characteristics with both

high sink and source capability. As inputs, Port E pins that are externally pulled low will

42073B-MCU Wireless-09/14

5

5 Page

ATmega2564/1284/644RFR2

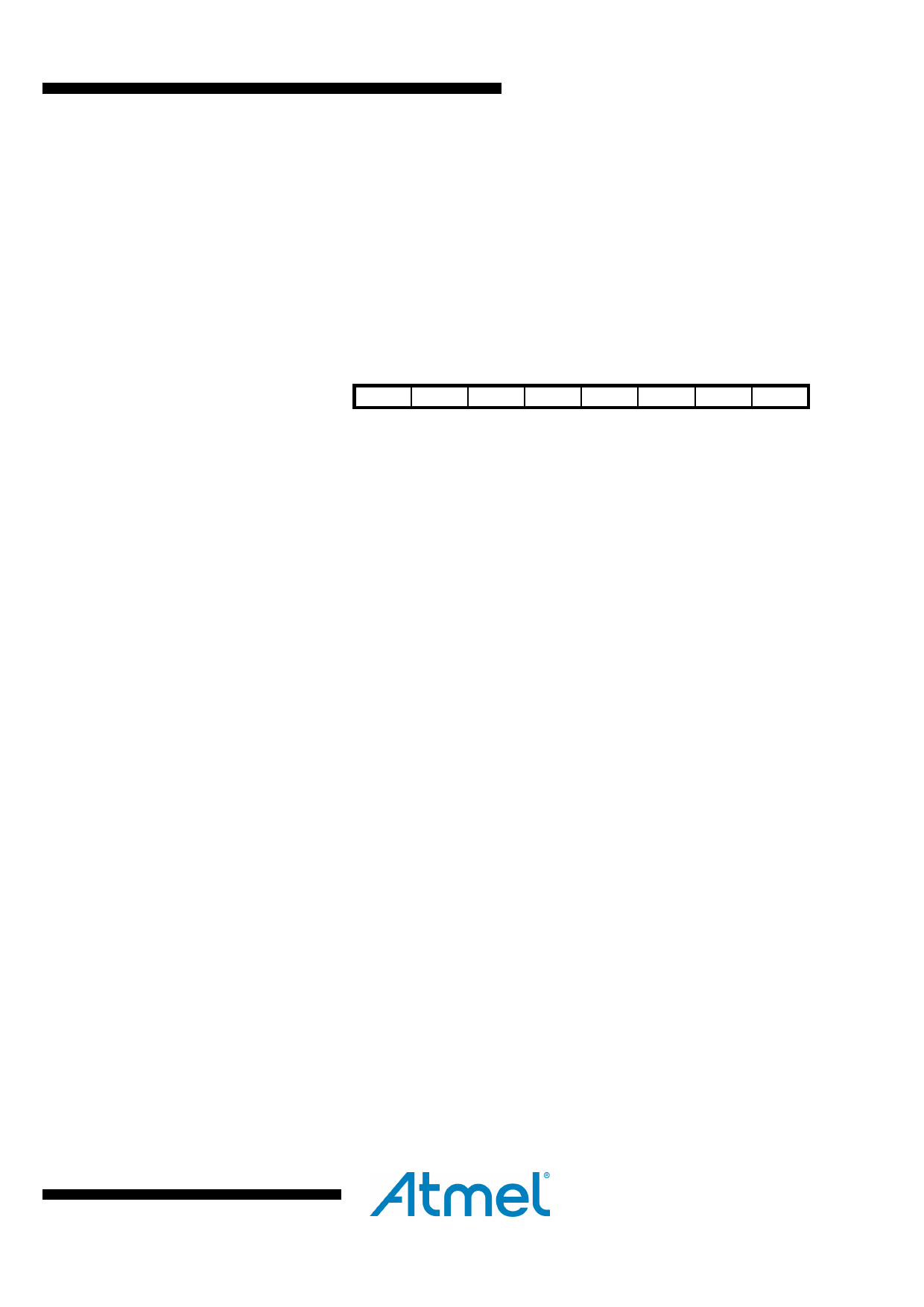

7.4 Status Register

The Status Register contains information about the result of the most recently executed

arithmetic instruction. This information can be used for altering program flow in order to

perform conditional operations. Note that the Status Register is updated after all ALU

operations, as specified in the Instruction Set Reference. This will in many cases

remove the need for using the dedicated compare instructions, resulting in faster and

more compact code. The Status Register is not automatically stored when entering an

interrupt routine and restored when returning from an interrupt. This must be handled by

software.

7.4.1 SREG – Status Register

Bit 7 6 5 4 3 2 1 0

$3F ($5F)

I

T H S V N Z C SREG

Read/Write RW RW RW RW RW RW RW RW

Initial Value

0

0

0

0

0

0

0

0

42073B-MCU Wireless-09/14

• Bit 7 – I - Global Interrupt Enable

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The

individual interrupt enable control is then performed in separate control registers. If the

global interrupt enable bit is cleared (zero), none of the interrupts are enabled

independent of the individual interrupt enable settings. The I-bit is cleared by hardware

after an interrupt has occurred, and is set by the RETI instruction to enable subsequent

interrupts.

• Bit 6 – T - Bit Copy Storage

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T bit as source

and destination for the operated bit. A bit from a register in the register file can be

copied into T by the BST instruction, and a bit in T can be copied into a bit in a register

in the register file by the BLD instruction.

• Bit 5 – H - Half Carry Flag

The half carry flag H indicates a half carry in some arithmetic operations. See the

Instruction Set Description for detailed information.

• Bit 4 – S - Sign Bit

The S-bit is always an exclusive or between the negative flag N and the two's

complement overflow flag V. See the Instruction Set Description for detailed

information.

• Bit 3 – V - Two's Complement Overflow Flag

The two's complement overflow flag V supports two's complement arithmetics. See the

Instruction Set Description for detailed information.

• Bit 2 – N - Negative Flag

The negative flag N indicates a negative result after the different arithmetic and logic

operations. See the Instruction Set Description for detailed information.

• Bit 1 – Z - Zero Flag

The zero flag Z indicates a zero result after the different arithmetic and logic operations.

See the Instruction Set Description for detailed information.

• Bit 0 – C - Carry Flag

The carry flag C indicates a carry in an arithmetic or logic operation. See the Instruction

Set Description for detailed information. Note that the status register is not automatically

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ATmega644RFR2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ATmega644RFR2 | 8-bit Microcontroller | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |