|

|

PDF ISL59911 Data sheet ( Hoja de datos )

| Número de pieza | ISL59911 | |

| Descripción | 250MHz Triple Differential Receiver/ Equalizer | |

| Fabricantes | Intersil | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ISL59911 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

250MHz Triple Differential Receiver/ Equalizer with I2C

Interface

ISL59911

The ISL59911 is a triple channel differential receiver and

equalizer optimized for RGB and YPbPr video signals. It

contains three high speed differential receivers with

programmable frequency compensation. The ISL59911

features manual or automatic offset calibration and ±4dB of

gain adjustment range with a resolution of 0.1dB.

The ISL59911 has a bandwidth of 250MHz and consumes only

110mA from a ±5V supply in normal operation.

When deasserted, the ENABLE pin puts the amplifiers into a

low power, high impedance state, minimizing power when not

needed and also allowing multiple devices to be connected in

parallel, allowing two or more ISL59911 devices to function as

a multiplexer.

The ISL59911 can also directly decode the sync signals

encoded onto the common modes of three pairs of Cat 5 cable

(by an ISL59311, EL4543, or similar device) or it can output

the actual common mode voltages for each of the three

channels.

The ISL59911 is available in a 32 Ld QFN package and is

specified for operation over the full -40°C to +85°C

temperature range.

Features

• 250MHz -3dB bandwidth

• 5 Adjustable EQ bands: 100MHz, 20MHz, 6MHz, 1MHz, and

200kHz

• 3rd-order lowpass filter at output with programmable corner

• ±4dB fine gain control with 0.1dB (7-bit) resolution

• Offset calibration minimizes output offset voltage

• Decodes HSYNC and VSYNC signals embedded in common

mode

• I2C interface with four unique addresses

• ±5V supplies @ 110mA

• 32 Ld 5mm x 6mm QFN package

Applications

• KVM monitor extension

• Digital signage

• General-purpose twisted-pair receiving and equalization

• High-resolution security video

ISL59311

OR

EL4543

TRIPLE

DIFFERENTIAL

VIDEO

DRIVER

UP TO 300m OF

CAT X CABLE

TERMINATION

NETWORK

1k 50

50

0.1µF 50

TERMINATION

NETWORK

TERMINATION

NETWORK

+5V +5V

RP RP

SYSTEM

MICRO-

CONTROLLER

I2C INTERFACE

+5V -5V

TWISTED-PAIR RGB VIDEO RECEIVER

CBYPASS*

x3

xC3BYPASS** Speaeg“ePo1w0efrorSmupoprley

Bypassing” on

information.

RIN+

RIN-

V+ V- and

THERMAL

PAD

ISL59911

ROUT

GOUT

BOUT

75 x3

GIN+

GIN-

BIN+

BIN-

ADDR0

ADDR1

RREF

GREF

BREF

HSOUT/RCM

VSOUT/GCM

ISL59920

ISL59921

ISL59922

or

ISL59923

VIDEO

DELAY

LINE

74HC04 or

SIMILAR

SCL

SDA

ENABLE

GND

BCM NC

FIGURE 1. TYPICAL APPLICATION CIRCUIT

September 2, 2011

FN7548.0

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 |Copyright Intersil Americas Inc. 2011. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

1 page

ISL59911

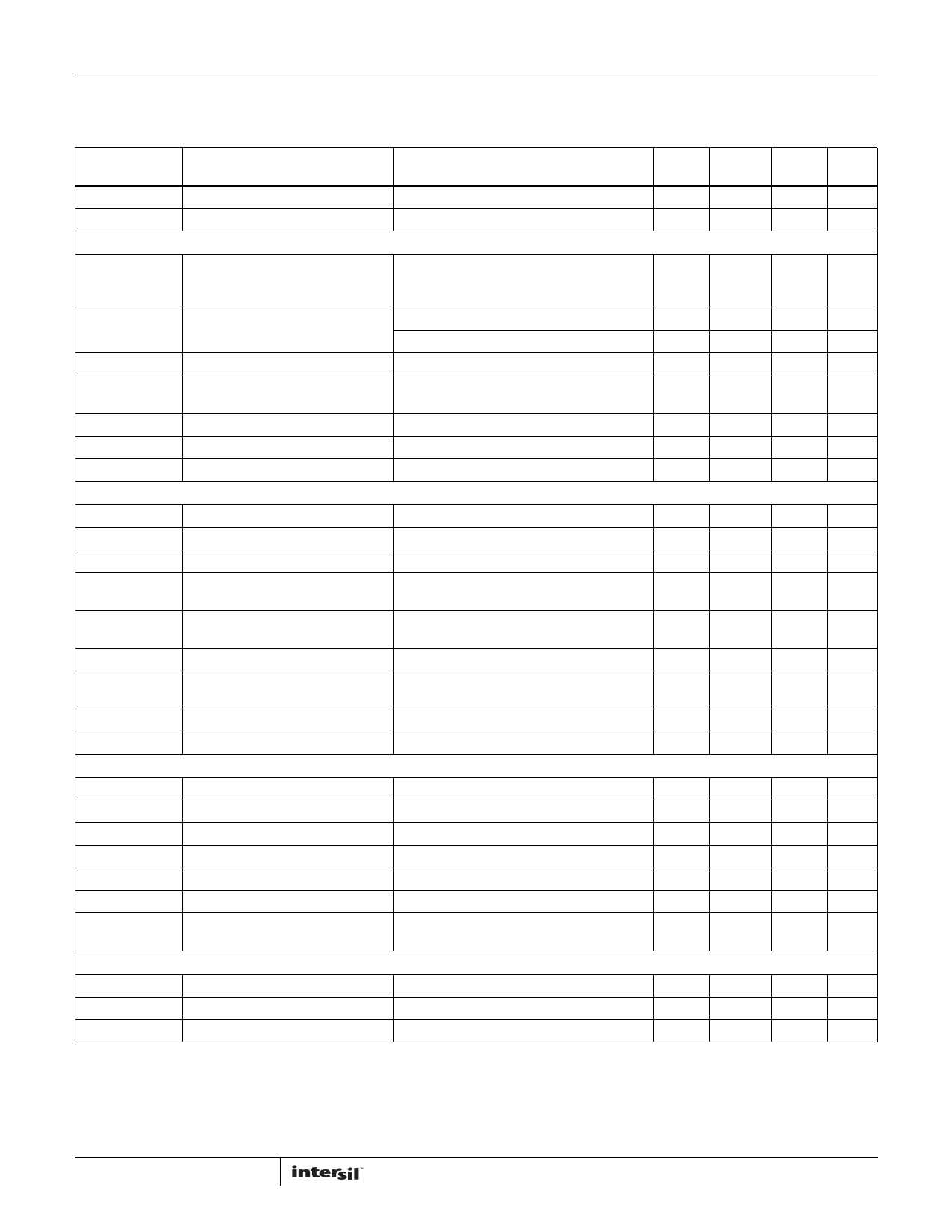

Electrical Specifications V+ = V+R = V+G = V+B = +5V, V- = V-R = V-G = V-B = V-D = -5V, TA = +25°C, all registers at default settings

(equalizer stages set to minimum boost, noise filter set to max bandwidth, x2 gain mode, GAINDC = 0dB), all analog inputs at 0V, auto offset

calibration executed, RL = 5pF || (75Ω + 75Ω) to GND, thermal pad connected to -5V, unless otherwise specified. (Continued)

PARAMETER

DESCRIPTION

CONDITIONS

MIN MAX

(Note 7) TYP (Note 7) UNIT

BWCM

Common Mode Amplifier Bandwidth

SRCM

Common Mode Slew Rate

INPUT CHARACTERISTICS

10k || 5pF load

VIN = -0.5V to +1.5V

24 MHz

0.1 V/ns

CMIR

Common-mode Input Range

Differential signal passed undistorted.

Effective headroom is reduced by the p-p

amplitude of differential swing divided by 2.

-3.2/+4.0

V

CMRR

Common-mode Rejection Ratio

Measured at 100kHz

88 dB

Measured at 10MHz

58 dB

CINDIFF

RINDIFF

Differential Input Capacitance

Differential Input Resistance

Capacitance between VINP and VINM

Resistance between VIN+ and VIN-

(due to common mode input resistance)

0.5 pF

20 kΩ

CINCM

CM Input Capacitance

Capacitance from VIN+ and VIN- to GND

1.3

RINCM

CM Input Resistance

Resistance from VIN+ and VIN- to GND

25

VINDIFF_P-P

Max P-P Differential Input Range

Delta VIN+ - VIN- when slope gain falls to 0.9

1.9

OUTPUT CHARACTERISTICS

pF

kΩ

V

VOUT

IOUT

V(VOUT)OS

R(VCM)

Output Voltage Swing

Output Drive Current

Output Offset Voltage

RL = 10Ω, VIN+ - VIN- = ±2V

Post-offset calibration

CM Output Resistance of VCM_R/G/B At 100kHz

(CM Output Mode)

±2.75

V

±22 mA

-20 -8 +5 mV

2.5 Ω

Gain

Gain

x1 mode

x2 mode

0.95 1.0 1.05 V/V

1.9 2.0 2.1

ΔGain

Channel-to-Channel Gain Mismatch x1 and x2 modes

±3 %

ONOISE

Integrated Noise at Output

Inputs @ GND through 50Ω.

0m of Equalization (Nominal)

300m of Equalization

4 mVRMS

20

SYNCOUTHI

SYNCOUTLO

SCL, SDA PINS

fMAX

VOL

VIH

VIL

VHYST

ILEAKAGE

tGLITCH

High Level output on VS/HSOUT

Low Level output on VS/HSOUT

10k || 5pF load, SYNC Output Mode

10k || 5pF load, SYNC Output Mode

Maximum I2C Operating Frequency

SDA Output Low Level

Input High Level

Input Low Level

Input Hysteresis

Input Leakage Current

Maximum Width of Glitch on SCL (or

SDA) Guaranteed to be Rejected

VSINK = 6mA

V+ - 1.5

400

3

0.55

50

V

0.4 V

kHz

0.4 V

V

1.5 V

V

±1 µA

ns

ENABLE, ADDR0, ADDR1 PINS

VIH Input High Level

3

VIL Input Low Level

ILEAKAGE

Input Leakage Current

NOTE:

7. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

V

0.8 V

±1 µA

5 FN7548.0

September 2, 2011

5 Page

ISL59911

Length

(m)

0

25

50

75

100

125

150

175

200

225

250

275

300

TABLE 1. Cat 5 LOOK-UP TABLE

Reg Reg Reg Reg

2345

0x00

0x00

0x00

0x00

0x20

0x11

0x10

0x00

0x24

0x22

0x21

0x01

0x25

0x33

0x31

0x01

0x49

0x44

0x42

0x01

0x69

0x55

0x53

0x02

0x89

0x75

0x62

0x02

0x92

0x86

0x72

0x04

0x96

0x96

0x82

0x06

0x97

0xA7

0x93

0x08

0xB7

0xB8

0xB2

0x09

0xD7

0xC9

0xC3

0x0A

0xF7

0xEA

0xD2

0x0C

Reg

6-8

0x40

0x40

0x44

0x44

0x48

0x48

0x4C

0x4C

0x50

0x50

0x54

0x54

0x58

Offset Calibration

Historically, programmable video equalizer ICs have had large

and varying offset voltages, often requiring external circuitry

and/or manual trim to reduce the offset to acceptable levels. The

ISL59911 improves upon this by adding an offset calibration

circuit that, when triggered by setting bit 0 of I2C register 0x0C,

shorts the inputs together internally, compares the ROUT, GOUT,

and BOUT voltages to their corresponding RREF, GREF, and BREF

voltages and uses a DAC with a successive-approximation

technique to minimize the delta between them (see Figure 12).

VIN+

VIN-

INPUT

BUFFER

EQ AND

GAIN

DAC

OUTPUT

BUFFER

VOUT

SAR

LOGIC

COMPARATOR

VREF

FIGURE 12. OFFSET CALIBRATION (ONE CHANNEL SHOWN)

When the ISL59911 is first powered up, the offset error is

undefined until an offset calibration is performed. The output

offset voltage of the ISL59911 also varies as the filter and gain

settings are adjusted. To minimize offset, always perform an

offset calibration after finalizing the filter and gain settings.

An offset calibration only takes about 3μs, so offset calibrations

can be performed after every register write without adding

significant time to the adjustment process. This minimizes offset

throughout the entire equalization adjustment procedure.

Output Signals

The ROUT, GOUT, and BOUT outputs can drive either a standard

75Ω video load in x1 gain mode or a 150Ω source-terminated

load (75Ω in series at source end [ISL59911 output pin], plus

75Ω termination to ground at receive end) in x2 mode. If the

output of the ISL59911 is going directly into an ISL59920 or

11

similar delay line, termination to ground is not necessary,

however, a ~75Ω series resistor at each output pin will help

isolate the outputs from the PCB trace capacitance, improving

the flatness of the frequency response.

When ENABLE is low, the ROUT, GOUT, and BOUT outputs are put

in a high-impedance state, allowing multiple ISL59911 devices

to be configured as a multiplexer by paralleling their outputs and

using ENABLE to select the active RGB channel.

Common Mode and HSYNC/VSYNC Outputs

In addition to the incoming differential video signals, the

ISL59911 also processes the common mode voltage on the

differential inputs and can output the signal in one of two ways

(as determined by the Output Configuration bit in register 0x01).

When the Output Configuration bit is set to 0 (the default), the

common mode input voltages are sent to comparators that

decode the voltage into HSYNC and VSYNC signals according to

the EL4543/ISL59311 standard encoding scheme shown in

Figure 13 and in Table 2 on page 11. The HSYNC signal appears

on the HSOUT/RCM pin, the VSYNC signal on VSOUT/GCM. The BCM

output pin is held at a logic low (0v).

To minimize noise coupling into the analog section from the sync

output drivers, the HSOUT and VSOUT outputs have limited current

drive, and should be buffered by 74HC04 or similar CMOS

buffers, as shown in Figure 1, before driving any significant loads

(such as a VGA cable).

When the Output Configuration bit is set to 1, buffered versions

of the three common mode input voltages are available on the

RCM, GCM, and BCM pins. Making the raw common mode signal

available allows for custom encoding schemes and/or

transmission of analog signals on the video signals’ common

mode.

3.0V

2.0V

3.0V

2.0V

3.0V

2.0V

2.5V

0V

2.5V

0V

BLUE CM

GREEN CM

RED CM

VSYNC

HSYNC

TIME (0.5ms/DIV)

FIGURE 13. H AND V SYNC SIGNAL ENCODING

RED CM

2.5V

3.0V

2.0V

2.5V

TABLE 2. H AND V SYNC DECODING

GREEN CM

3.0V

BLUE CM

2.0V

HSYNC

Low

2.0V 2.5V Low

3.0V 2.5V High

2.0V 3.0V High

VSYNC

Low

High

Low

High

FN7548.0

September 2, 2011

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet ISL59911.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ISL59910 | (ISL59910 / ISL59913) Triple Differential Receiver/Equalizer | Intersil Corporation |

| ISL59911 | 250MHz Triple Differential Receiver/ Equalizer | Intersil |

| ISL59913 | (ISL59910 / ISL59913) Triple Differential Receiver/Equalizer | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |