|

|

PDF NOII5SM1300A Data sheet ( Hoja de datos )

| Número de pieza | NOII5SM1300A | |

| Descripción | IBIS5 1.3 Megapixel CMOS Image Sensor | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NOII5SM1300A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

NOII5SM1300A

IBIS5 1.3 Megapixel CMOS

Image Sensor

Features

• 1280 x 1024 Active Pixels

• 6.7 mm x 6.7 mm Square Pixels

• 2/3” Optical Format

• Global and Rolling Shutter

• Master Clock: 40 MHz

• 27 fps (1280 x 1024) and 106 fps (640 x 480)

• On-chip 10-bit ADCs

• Serial Peripheral Interface (SPI)

• Windowing (ROI)

• Sub-sampling: 1:2 Mode

• Supply Voltage

♦ Analog: 3.0 V to 4.5 V

♦ Digital: 3.3 V

♦ I/O: 3.3 V

• Power Consumption: 200 mW

• −30°C to +65°C Operating Temperature Range

• 84-pin LCC Package

• These Devices are Pb−Free and are RoHS Compliant

Applications

• Machine Vision

• Inspection

• Robotics

• Traffic Monitoring

http://onsemi.com

Figure 1. IBIS5−1300 Photo

Description

The IBIS5-1300 is a solid state CMOS image sensor that integrates the functionality of complete analog image acquisition,

digitizer, and digital signal processing system on a single chip. This 1.3-mega pixel (1280 x 1024) CMOS active pixel sensor

dedicated to industrial vision applications features both rolling and snapshot (or global) shutter. Full frame readout time is

36 ms (max. 27.5 fps), and readout speed are boosted by windowed region of interest (ROI) readout. Another feature includes

the double and multiples slope functionality to capture high dynamic range scenes. The sensor is available in a monochrome

version or Bayer (RGB) patterned color filter array.

User programmable row and column start/stop positions allow windowing down to a 2x1 pixel window for digital zoom.

Sub sampling or viewfinder mode reduces resolution while maintaining the constant field of view and an increased frame

rate. An on-chip analog signal pipeline processes the analog video output of the pixel array. Double sampling (DS) eliminates

the fixed pattern noise. The programmable gain and offset amplifier maps the signal swing to the ADC input range. A 10-bit

ADC converts the analog data to a 10-bit digital word stream. The sensor uses a 3-wire serial peripheral interface (SPI), or a

16-bit parallel interface. It operates with a 3.3 V power supply and requires only one master clock for operation up to 40 MHz.

It is housed in an 84-pin ceramic LCC package.

ORDERING INFORMATION

Marketing Part Number

Description

NOII5SM1300A-QDC

Mono with glass

NOII5SM1300A-QWC

NOII5SC1300A-QDC

Mono without glass

Color with glass

NOII5FM1300A-QDC

Mono on thicker epitaxial layer, with glass

NOTE: See Ordering Code Information on page 33 for more information.

Package

84−pin LCC

Device Status

End−of−Life (EOL)

Last Time Buy

PCN Close date:

October 29, 2011

© Semiconductor Components Industries, LLC, 2013

May, 2013 − Rev. 12

1

Publication Order Number:

NOII5SM1300A/D

1 page

NOII5SM1300A

ARCHITECTURE AND OPERATION

This section presents detailed information about the most important sensor blocks

Imager core

Sensor

Y−left

addressing

Pixel

Y-right

addressing

Reset

C

Sample

Select

Column output

Pixel core

Column amplifiers

Analog multiplexer

X−addressing

Output

amplifier

Sequencer

ADC

System clock

40 MHz

External

connection

Figure 2. Block Diagram of IBIS5−1300 Image Sensor

Floor Plan

Figure 2 shows the architecture of the IBIS5-1300 image

sensor. It consists basically of a pixel array, one X- and two

Y-addressing registers for the readout in X- and Y-direction,

column amplifiers that correct for the fixed pattern noise, an

analog multiplexer, and an analog output amplifier

Use the left Y-addressing register for readout operation.

Use the right Y-addressing register for reset of pixel rows. In

multiple slope synchronous shutter mode, the right

Y-addressing register resets the whole pixel core with a

lowered reset voltage. In rolling curtain shutter mode, use

the right Y-addressing register for the reset pointer in single

and double slope operation to reset one pixel row.

The on-chip sequencer generates most of the signals for

the image core. Some basic signals (such as start/stop

integration, line and frame sync signals) are generated

externally.

A 10-bit ADC is implemented on chip but electrically

isolated from the image core. You must route the analog

pixel output to the analog ADC input on the outside.

http://onsemi.com

5

5 Page

NOII5SM1300A

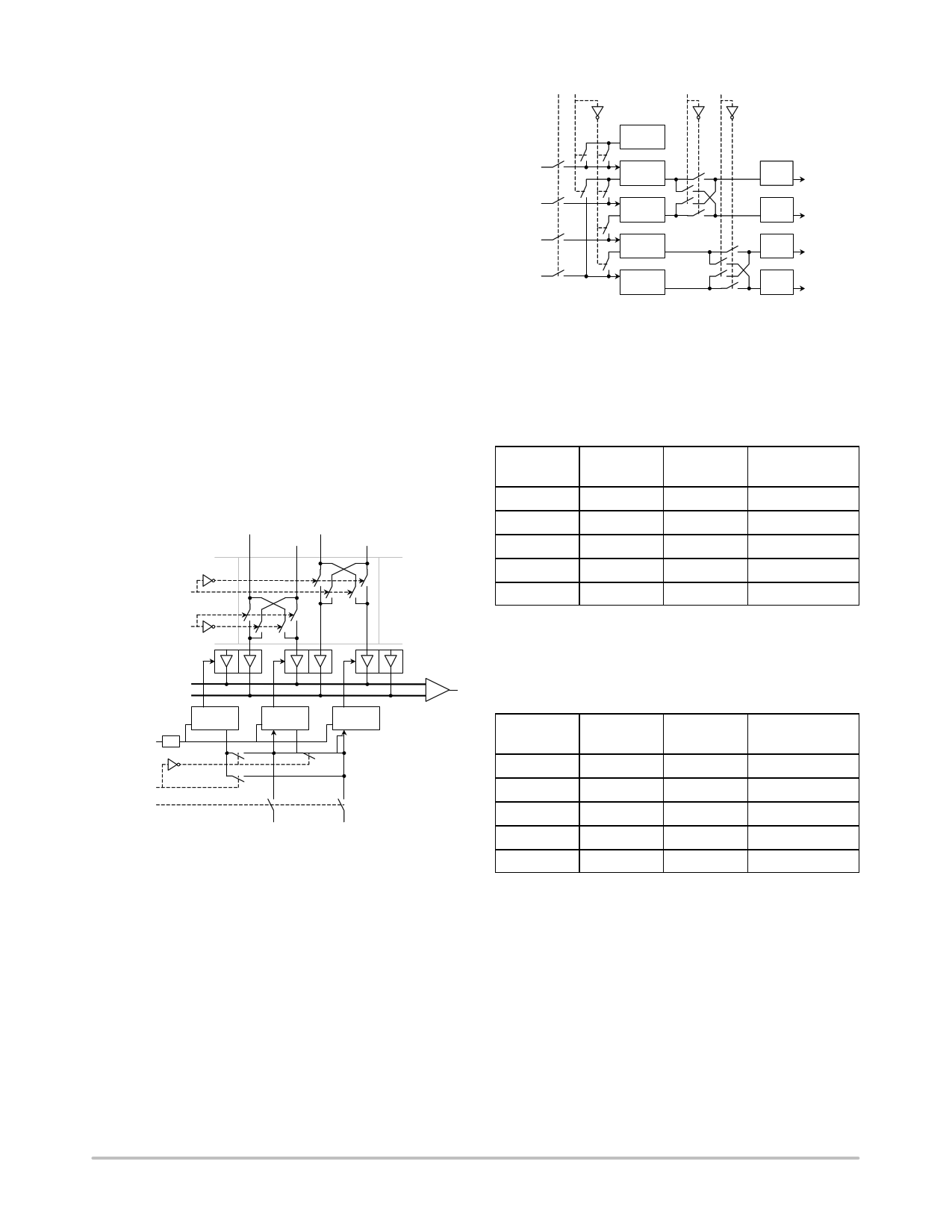

X−Addressing

Because of the high pixel rate, the X-shift register selects

two columns at a time for readout, so it runs at half the

system clock speed. All even columns are connected to

bus A; all odd columns to bus B. In the output amplifier,

bus A and bus B are combined into one stream of pixel data

at system clock speed.

At the end of the row blanking time, the X_SYNC switch

is closed while all other switches are open and the decoder

output is fed to the register. The decoder loads a logical one

in one of the registers and a logical zero in the rest. This

defines the starting point of the window in the X direction.

As soon as the X_SYNC signal is released, the register starts

shifting from the start position.

When no sub-sampling is required, X_SUB is inactive.

The pointer in the shift-register moves one bit at a time.

When sub-sampling is enabled, X_SUB is activated. The

shift register moves two bits at a time. Taking into account

that every register selects two columns, hence two pixels

sub-sampling results in the pattern ‘XXOOXXOO’ when

eight pixels are considered. Suppose the columns are

numbered from left to right starting with 0 (zero) and

sub-sampling is enabled:

COL(i )

COL (i+2)

COL(i+1)

COL(i+3)

X_SW AP30

X_SW AP12

BUS_A

BUS_B

AB

Reg(n)

SYS_CLOCK 1/2

AB

Reg(n+1)

AB

Reg(n+2)

Column

amplifiers

Output

amplifier

X_SUB

X_SYNC

DEC(n+1) DEC(n+2)

Figure 9. Column Structure

If columns 1 and 2, 5 and 6, 9 and 10 … are swapped using

the SWAP_12 switches, a normal sub-sampling pattern of

‘XOXOXOXO’ is obtained.

If columns 3 and 4, 7 and 8, 11 and 12 … are swapped

using the SWAP_30 switches, the pattern is

‘OXOXOXOX’.

If both the SWAP_12 and SWAP_30 switches are closed,

pattern ‘OOXXOOXX’ is obtained.

Y_SYNC Y_SUB

Y_SW AP12 Y_SW AP30

Reg(n)

DEC(n+1)

Reg(n+1)

SRH ROW(n+1)

DEC(n+2)

Reg(n+2)

SRH

ROW(n+2)

DEC(n+3)

Reg(n+3)

SRH ROW(n+3)

DEC(n+4)

Reg(n+4)

SRH ROW(n+4)

Figure 10. Row Structure

Because every register addresses two columns at a time,

the addressable pixels range in sub-sample mode is from

zero to half the maximum number of pixels in a row (only

even values). For instance: 0, 2, 4, 6, 8… 638.

Table 11. X–SUB-SAMPLING PATTERNS

X_SUB

X_SWAP12 X_SWAP30

Sub-Sample

Pattern

0 0 0 XXXXXXXX

1 0 0 XXOOXXOO

1 1 0 XOXOXOXO

1 0 1 OXOXOXOX

1 1 1 OOXXOOXX

Y−Addressing

For symmetry reasons, the sub-sampling modes in the

Y-direction are the same as in X-direction.

Table 12. Y–SUB-SAMPLING PATTERNS

Y_SUB

Y_SWAP12 Y_SWAP30

Sub-Sample

Pattern

0 0 0 XXXXXXXX

1 0 0 XXOOXXOO

1 1 0 XOXOXOXO

1 0 1 OXOXOXOX

1 1 1 OOXXOOXX

In normal mode, the pointer for the pixel row is shifted one

at a time.

When sub-sampling is enabled, Y_SYNC is activated.

The Y-shift register shifts 2 succeeding bits and skips the 2

next bits. This results in pattern ‘XXOOXXOO’.

Activating Y_SWAP12 results in pattern

‘XOXOXOXO’.

Activating Y_SWAP30 results in pattern

‘OXOXOXOX’.

Activating both Y_SWAP12 and Y_SWAP30 results in

pattern ‘OOXXOOXX’.

The addressable pixel range when Y-sub sampling is

enabled is: 0–1, 4–5, 8–9, 12–13, … 1020–1021

http://onsemi.com

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet NOII5SM1300A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NOII5SM1300A | IBIS5 1.3 Megapixel CMOS Image Sensor | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |