|

|

PDF NPIC6C595 Data sheet ( Hoja de datos )

| Número de pieza | NPIC6C595 | |

| Descripción | Power logic 8-bit shift register | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NPIC6C595 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

NPIC6C595

Power logic 8-bit shift register; open-drain outputs

Rev. 1 — 20 August 2012

Product data sheet

1. General description

The NPIC6C595 is an 8-bit serial-in/serial or parallel-out shift register with a storage

register and open-drain outputs. Both the shift and storage register have separate clocks.

The device features a serial input (DS) and a serial output (Q7S) to enable cascading and

an asynchronous reset input (MR). A LOW on MR resets both the shift register and

storage register. Data is shifted on the LOW-to-HIGH transitions of the SHCP input. The

data in the shift register is transferred to the storage register on a LOW-to-HIGH transition

of the STCP input and to the Q7S output on a LOW-to-HIGH transition of the SHCP input.

If both clocks are connected together, the shift register is always one clock pulse ahead of

the storage register. Data in the storage register drives the gate of the output

extended-drain NMOS transistor whenever the output enable input (OE) is LOW. A HIGH

on OE causes the outputs to assume a high-impedance OFF-state. Operation of the OE

input does not affect the state of the registers. The open-drain outputs are 33 V/100 mA

continuous current extended-drain NMOS transistors designed for use in systems that

require moderate load power such as LEDs. Integrated voltage clamps in the outputs

provide protection against inductive transients. This feature makes the device suitable for

power driver applications such as relay, solenoids and other low-current or

medium-voltage loads.

2. Features and benefits

Specified from 40 C to +125 C

Low RDSon

Eight Power EDNMOS transistor outputs of 100 mA continuous current

250 mA current limit capability

Output clamping voltage 33 V

30 mJ avalanche energy capability

All registers cleared with single input

Low power consumption

ESD protection:

HBM JDS-001 Class 2 exceeds 2500 V

CDM JESD22-C101E exceeds 1000 V

3. Applications

LED sign

Graphic status panel

Fault status indicator

1 page

NXP Semiconductors

NPIC6C595

Power logic 8-bit shift register; open-drain outputs

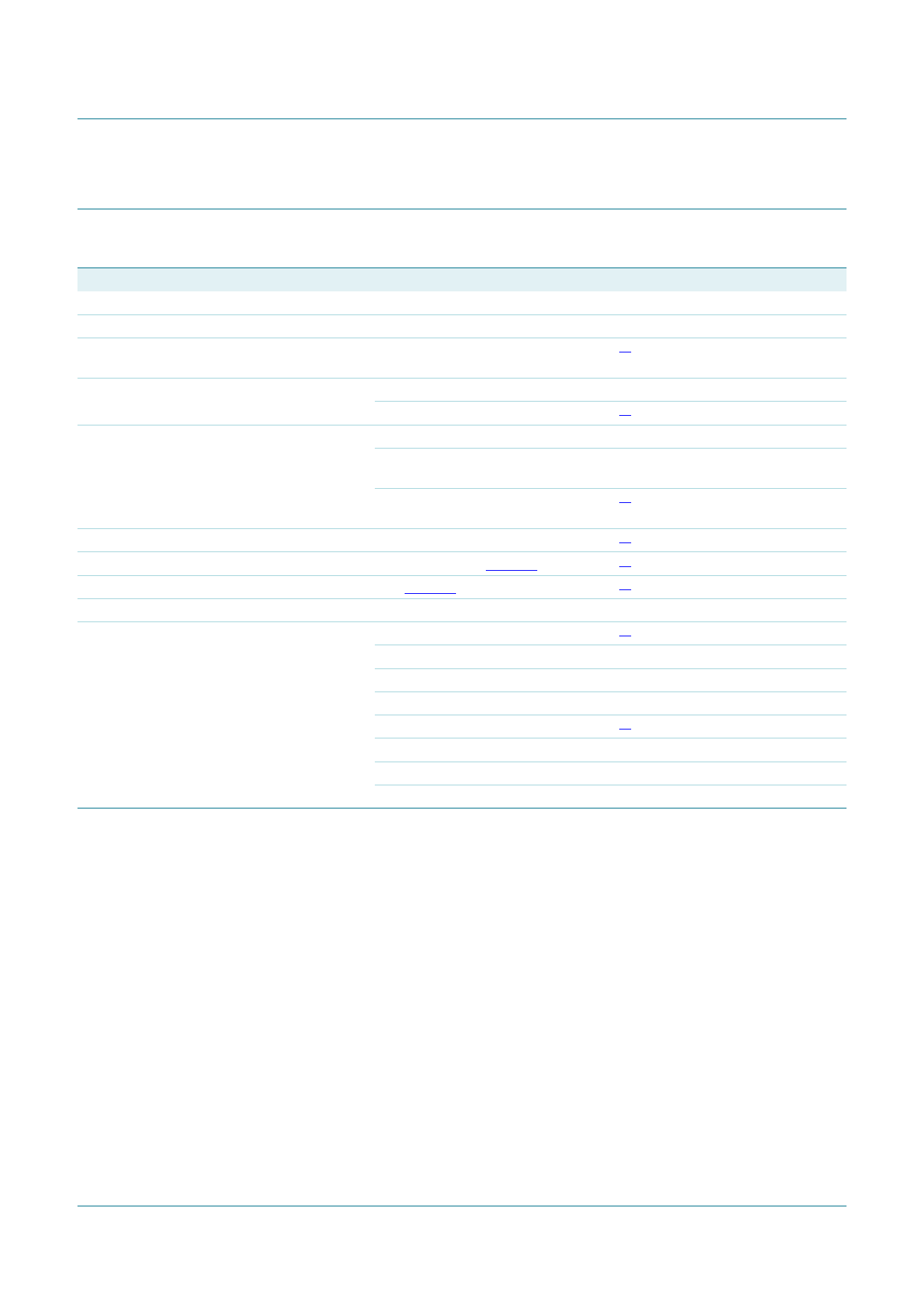

7. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol

Parameter

Conditions

Min Max

Unit

VCC supply voltage

VI input voltage

VDS drain-source voltage

power EDNMOS drain-source

voltage

0.5

0.3

[1] -

+7.0

+7.0

+33

V

V

V

Id(SD)

source-drain diode current

continuous

pulsed

-

[2] -

250

500

mA

mA

ID drain current

Tamb = 25 C

continuous; each output;

all outputs on

- 100

mA

pulsed; each output;

all outputs on

[2] -

250

mA

IDM peak drain current

single output; Tamb = 25 C

EAS non-repetitive avalanche energy single pulse; see Figure 9

IAL avalanche current

see Figure 9

Tstg storage temperature

Ptot total power dissipation Tamb = 25 C

SO16

[2] -

[3] -

[3] -

65

[4]

-

250

30

200

+150

800

mA

mJ

mA

C

mW

TSSOP16

- 725

mW

DHVQFN16

- 1825

mW

Tamb = 125 C

SO16

[4]

-

160

mW

TSSOP16

- 145

mW

DHVQFN16

- 365

mW

[1] Each power EDNMOS source is internally connected to GND.

[2] Pulse duration 100 s and duty cycle 2 %.

[3] VDS = 15 V; starting junction temperature (Tj) = 25 C; L = 1.5 H; avalanche current (IAL) = 200 mA.

[4] For SO16 packages: above 25 C the value of Ptot derates linearly with 6.4 mW/C.

For TSSOP16 packages: above 25 C the value of Ptot derates linearly with 5.8 mW/C.

For DHVQFN16 packages: above 25 C the value of Ptot derates linearly with 14.6 mW/C.

NPIC6C595

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 1 — 20 August 2012

© NXP B.V. 2012. All rights reserved.

5 of 20

5 Page

NXP Semiconductors

NPIC6C595

Power logic 8-bit shift register; open-drain outputs

VI

negative

pulse

0V

VI

positive

pulse

0V

90 %

10 %

VM

10 %

tf

tr

90 %

VM

tW

tW

VM

tr

tf

VM

WORD

GENERATOR (1)

5V

7

MR

1

VCC

15

SHCP

2

DS

10

STCP

8

OE GND

16

VDS = 15 V

RL

3, 4, 5, 6

Qn 11, 12,13, 14

CL (2)

aaa-002561

(1) The word generator has the following characteristics: tr, tf 10 ns; tW = 300 ns; pulsed repetition rate (PRR) = 5 kHz; ZO = 50 .

(2) CL includes probe and jig capacitance.

Test data is given in Table 9. Definitions for test circuit:

VDS = External voltage for Power EDNMOS drain-source voltage.

RL = Load resistance.

CL = Load capacitance including jig and probe capacitance.

Fig 14. Test circuit for measuring switching times

Table 9. Test data

Supply voltage Input

VI

5V 5V

tr, tf

10 ns

VM

50 %

Load

CL

30 pF

RL

200

NPIC6C595

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 1 — 20 August 2012

© NXP B.V. 2012. All rights reserved.

11 of 20

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet NPIC6C595.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NPIC6C595 | Power logic 8-bit shift register | NXP Semiconductors |

| NPIC6C596 | Power logic 8-bit shift register | NXP Semiconductors |

| NPIC6C596A | Power logic 8-bit shift register | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |